One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## Scalable, Connected Precision Meter Platform with Intelligence

### SCOPE

This reference manual provides a detailed description of the ADuCM350 functionality and features.

#### Disclaimer

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

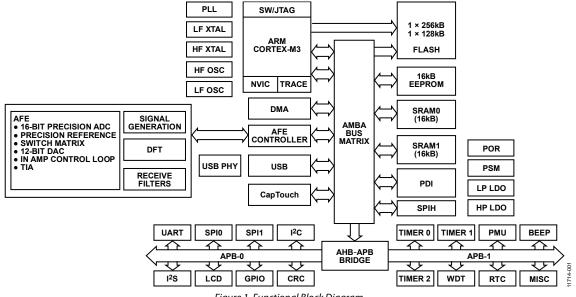

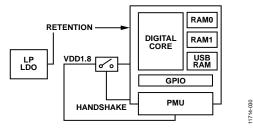

### FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

# TABLE OF CONTENTS

| Scope                                          |

|------------------------------------------------|

| Functional Block Diagram 1                     |

| Revision History                               |

| Introduction                                   |

| System Features7                               |

| System Block Diagram                           |

| Memory Organization9                           |

| Identification Registers10                     |

| ARM Cortex-M3 Core11                           |

| Features11                                     |

| Functional Description11                       |

| Debug Interface                                |

| Introduction13                                 |

| Debug Protocol Options13                       |

| Interface Access                               |

| Debug Features Supported13                     |

| Embedded Trace                                 |

| Features14                                     |

| Trace Implementation14                         |

| Trace Output14                                 |

| System Clocks                                  |

| Features                                       |

| Operation16                                    |

| Internal RC and External XTAL Oscillators      |

| Example Use Cases                              |

| System Clocks Memory Mapped Registers          |

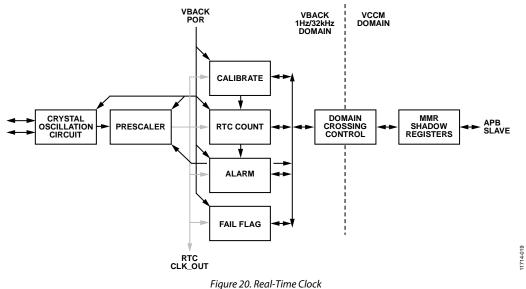

| Real-Time Clock                                |

| Summary                                        |

| Features                                       |

| Block Diagram                                  |

| Operation                                      |

| RTC Trimming                                   |

| Recommendations for Using the RTC              |

| RTC Memory Mapped Registers41                  |

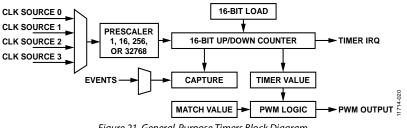

| General-Purpose Timers                         |

| Features                                       |

| Block Diagram                                  |

| Operation                                      |

| General-Purpose Timers Memory Mapped Registers |

|                                                |

| Register Summary: GPT1                   | 52        |

|------------------------------------------|-----------|

| Register Summary: GPT2                   | 55        |

| Wake-Up Timer (WUT)                      | 58        |

| Features                                 | 58        |

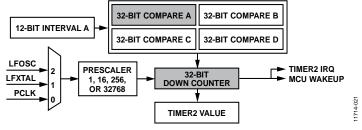

| Block Diagram                            | 58        |

| Operation                                | 58        |

| Interval Register                        | 58        |

| WUT Memory Mapped Registers              | 59        |

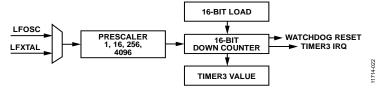

| Watchdog Timer (WDT)                     | 73        |

| Features                                 | 73        |

| Block Diagram                            | 73        |

| Operation                                | 73        |

| WDT Memory Mapped Registers              | 74        |

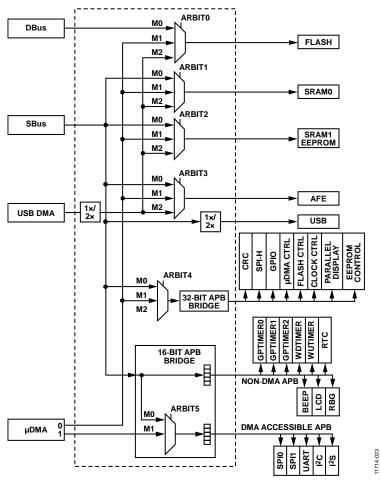

| Bus Matrix                               | 77        |

| Features                                 | 77        |

| Architecture                             | 78        |

| Operation                                | 78        |

| Bus Matrix Memory Mapped Registers       | 79        |

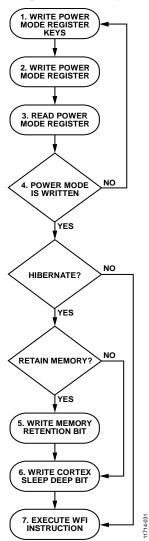

| Power Management Unit                    | 82        |

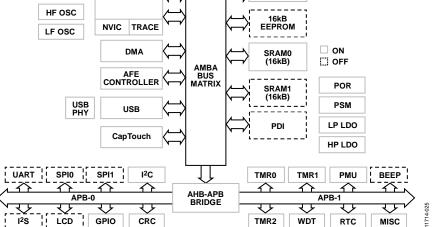

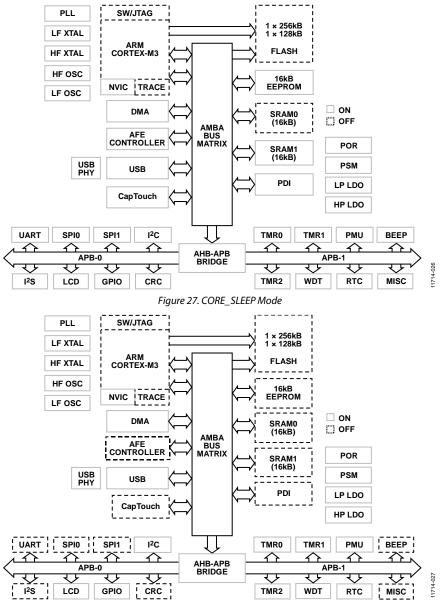

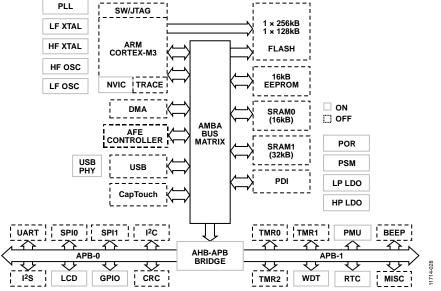

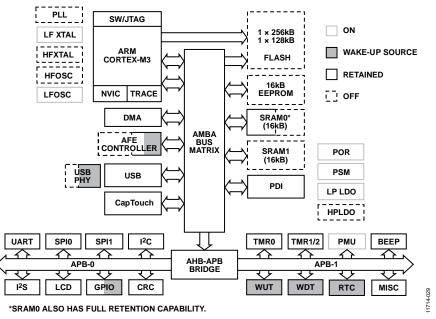

| Introduction                             | 82        |

| Power Modes                              | 83        |

| Power Mode Control Table                 | 86        |

| Wake-Up                                  | 87        |

| Power Gating                             | <u>89</u> |

| Power Gated Modules                      | <u>89</u> |

| Example Use Case                         | 90        |

| PMU Memory Mapped Registers              | 91        |

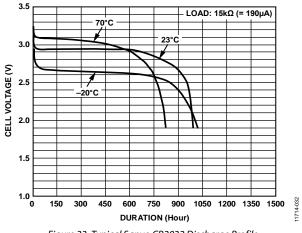

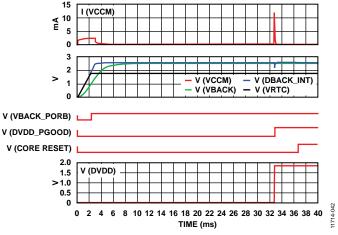

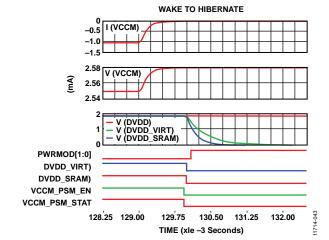

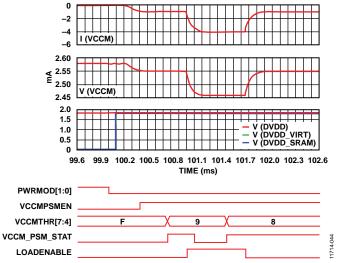

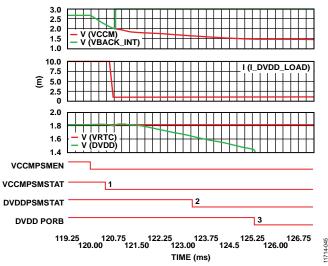

| Power Supplies                           | 92        |

| Introduction                             | 92        |

| Power Supply Sources                     | 93        |

| Power Supply Considerations              | 94        |

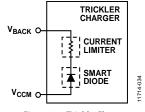

| Trickle Charger                          | 94        |

| Power Supply Modes                       | 94        |

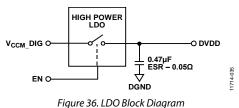

| High Power LDO                           | 94        |

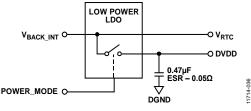

| Low Power LDO                            | 95        |

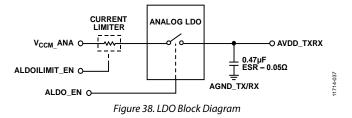

| Analog LDO                               | 95        |

| Supply Monitors                          | 95        |

| Power-On Reset Circuits                  | 98        |

| Power Cases                              | 98        |

| Power Supplies Memory Mapped Registers10 | 02        |

# ADuCM350 Hardware Reference Manual

| System Interrupts and Exceptions 105                        |

|-------------------------------------------------------------|

| ARM Cortex-M3 Exceptions 105                                |

| Nested Vectored Interrupt Controller (NVIC) 105             |

| Handling Interrupt Registers106                             |

| External Interrupt Configuration 107                        |

| System Interrupts Memory Mapped Registers 107               |

| Reset 112                                                   |

| Reset Operation112                                          |

| Reset Memory Mapped Registers 112                           |

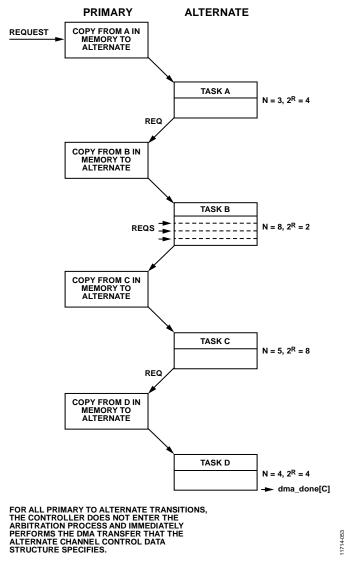

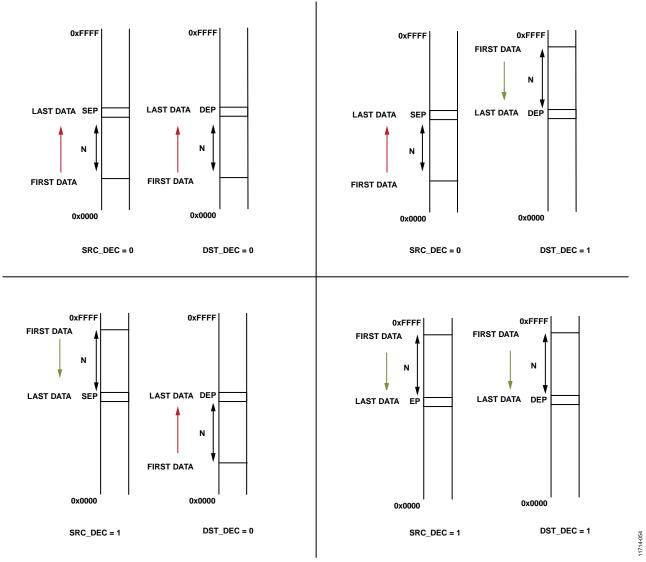

| DMA Controller 113                                          |

| Features                                                    |

| GPFDMACTL Register 114                                      |

| Operation 114                                               |

| DMA Controller Memory Mapped Registers 128                  |

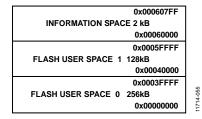

| Flash Controller                                            |

| Features                                                    |

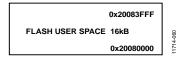

| Flash Memory Organization 135                               |

| Flash Integrity, Parity Feature for User Space 0            |

| Flash Integrity, Parity Feature for User Space 1            |

| Parity Error Interrupt140                                   |

| Abort Using System Interrupts141                            |

| Power-Down Instructions                                     |

| Flash Crash142                                              |

| Performance, Command Duration142                            |

| Flash Controller Memory Mapped Registers 143                |

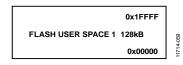

| General-Purpose Flash Controller 155                        |

| Features155                                                 |

| Flash Memory Organization155                                |

| Flash Integrity, Signature Feature 156                      |

| Bus Interface 156                                           |

| DMA Interface Feature157                                    |

| Abort Using System Interrupts 157                           |

| Power-Down Instructions                                     |

| Flash Crash 158                                             |

| Performance, Command Duration158                            |

| General-Purpose Flash Controller Memory Mapped<br>Registers |

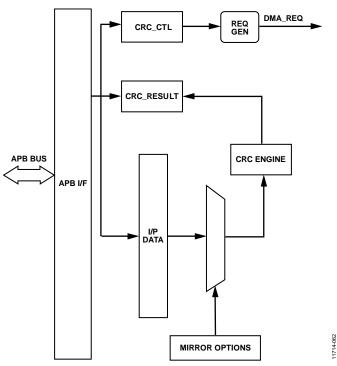

| CRC Accelerator                                             |

| Introduction163                                             |

| Features                                                    |

| Block Diagram 163                                           |

|                                                             |

| Operation                                       | 163 |

|-------------------------------------------------|-----|

| Programming Model                               | 164 |

| Core Access                                     | 164 |

| DMA Access                                      | 164 |

| Recommendations                                 | 165 |

| Mirroring Options                               |     |

| Signature Processing                            | 166 |

| CRC Accelerator Memory Mapped Registers         | 167 |

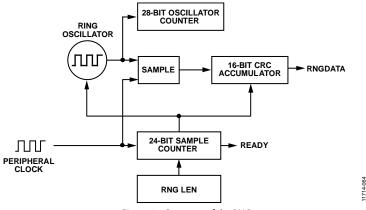

| Random Number Generator                         | 168 |

| Description                                     | 168 |

| RNG Architecture                                | 168 |

| RNG Oscillator Counter                          | 168 |

| RNG Entropy and Suprisal                        | 169 |

| Timer Mode                                      | 170 |

| Power-Down Considerations                       | 170 |

| RNG Memory Mapped Registers                     | 171 |

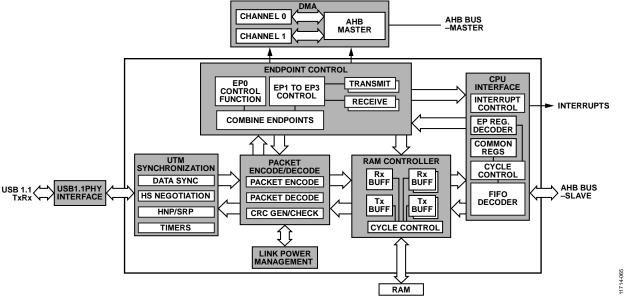

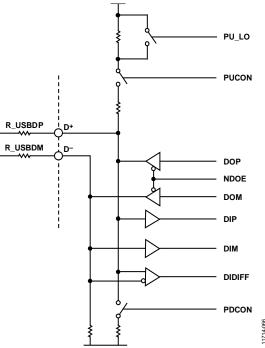

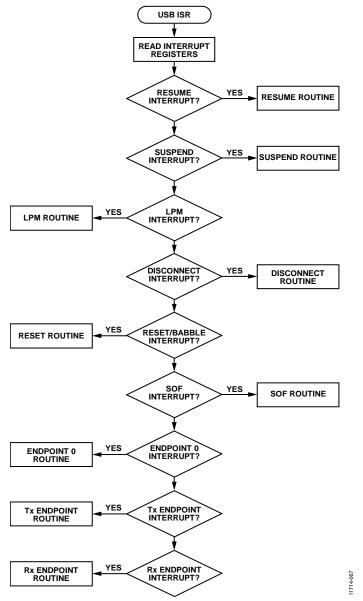

| Universal Serial Bus Controller                 | 173 |

| Features                                        | 173 |

| Architecture                                    | 174 |

| Operation                                       | 176 |

| Programming Scheme                              | 178 |

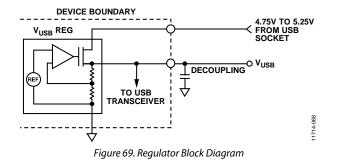

| USB Regulator                                   | 181 |

| USB Register Exceptions                         | 181 |

| Full Speed USB Device Controller (FSUSB) Memory |     |

| Registers                                       |     |

| UART                                            |     |

| Features                                        |     |

| Operation                                       | 213 |

| UART Memory Mapped Registers                    | 215 |

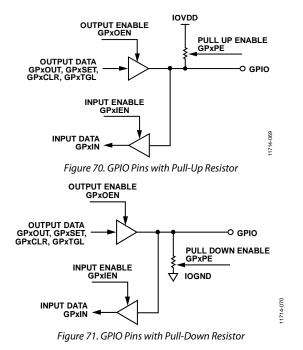

| GPIOs                                           |     |

| Functionality                                   |     |

| GPIO Control                                    | 220 |

| Block Diagram                                   | 220 |

| Operation                                       | 220 |

| System Clocks                                   | 222 |

| GPIO Memory Mapped Registers                    | 222 |

| I <sup>2</sup> C Serial Interface               | 240 |

| Functionality                                   | 240 |

| Operation                                       | 240 |

| I <sup>2</sup> C Memory Mapped Registers        | 244 |

| Serial Peripheral Interfaces (SPI)              | 253 |

UG-587

# UG-587

|                | Features                                            | 253 |

|----------------|-----------------------------------------------------|-----|

|                | Operation                                           | 253 |

|                | SPI Transfer Initiation                             | 254 |

|                | SPI Interrupts                                      | 255 |

|                | Wired-OR Mode (WOM)                                 | 256 |

|                | SPI DMA                                             | 256 |

|                | SPI and Power-Down Modes                            | 257 |

|                | SPIH vs. SPI0/SPI1                                  | 257 |

|                | SPI Memory Mapped Registers                         | 258 |

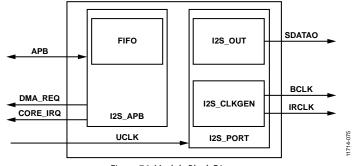

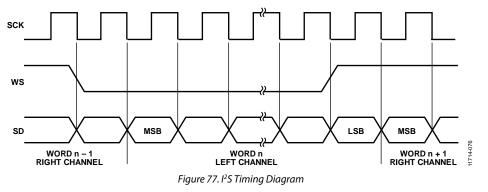

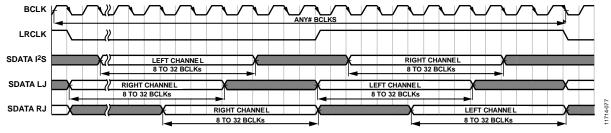

| I <sup>2</sup> | S Interface                                         | 262 |

|                | Features                                            | 262 |

|                | Module Architecture                                 | 262 |

|                | Operation                                           | 262 |

|                | I <sup>2</sup> S Interface                          | 263 |

|                | I <sup>2</sup> S Modes                              | 264 |

|                | Clock Generator                                     | 264 |

|                | I <sup>2</sup> S Transfer Initiation                | 264 |

|                | I <sup>2</sup> S Interrupts                         | 265 |

|                | I <sup>2</sup> S DMA                                | 265 |

|                | I <sup>2</sup> S Driver Example Configuration       | 266 |

|                | I <sup>2</sup> S Memory Mapped Registers            | 267 |

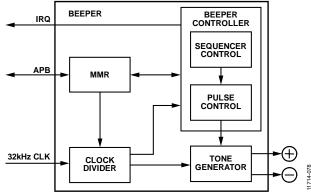

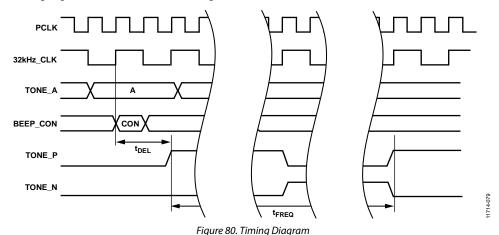

| В              | eeper Driver                                        | 272 |

|                | Features                                            | 272 |

|                | Module Architecture                                 | 272 |

|                | Operation                                           | 272 |

|                | Modes                                               | 273 |

|                | Pulse Mode                                          | 273 |

|                | Sequence Mode                                       | 273 |

|                | Tones                                               | 273 |

|                | Interrupts and Events                               | 274 |

|                | Clocking and Power                                  | 274 |

|                | Power-Down Considerations                           | 274 |

|                | Timing Diagram                                      | 275 |

|                | Programming Examples                                | 275 |

|                | Beeper Driver Memory Mapped Registers               | 276 |

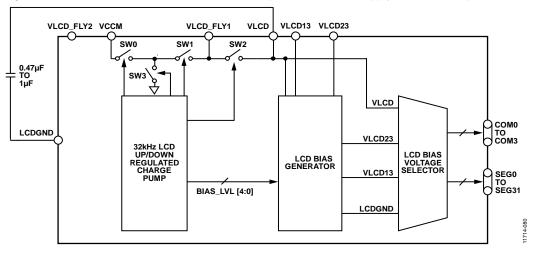

| L              | CD Controller                                       | 279 |

|                | Features                                            | 279 |

|                | LCD Software Setup                                  | 279 |

|                | LCD Charge Pump and External Capacitor Requirements | 279 |

|                | LCD Multiplex Types                                 | 280 |

|                | LCD Bias Types                                      |     |

|                |                                                     |     |

# ADuCM350 Hardware Reference Manual

| LCD Screen Selection                                                                              | ) |

|---------------------------------------------------------------------------------------------------|---|

| LCD Bias Voltage                                                                                  | ) |

| LCD Timing and Waveforms                                                                          | ) |

| Blink Mode                                                                                        | 1 |

| Operation During ADuCM350 Power Modes                                                             | 2 |

| Display Element Control                                                                           | 2 |

| LCD Memory Mapped Registers                                                                       | 4 |

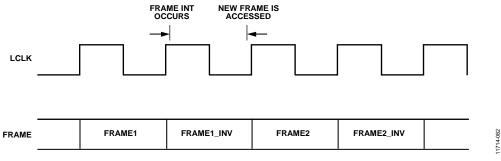

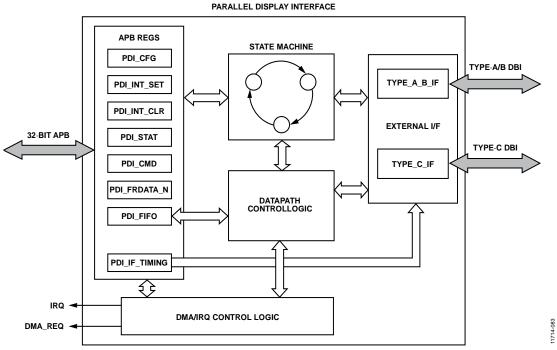

| Parallel Display Interface (PDI)                                                                  | 7 |

| Features                                                                                          | 7 |

| Not Supported                                                                                     | 7 |

| Byte Packing of Pixel Data                                                                        | 7 |

| Block Diagram                                                                                     | 8 |

| Pin List                                                                                          | 9 |

| Functional Operation                                                                              | 9 |

| Programming DBI Commands                                                                          | 9 |

| Pseudocode Example                                                                                | 1 |

| DMA Bandwidth Analysis for Video Data                                                             | 2 |

| PDI Memory Mapped Registers                                                                       | 2 |

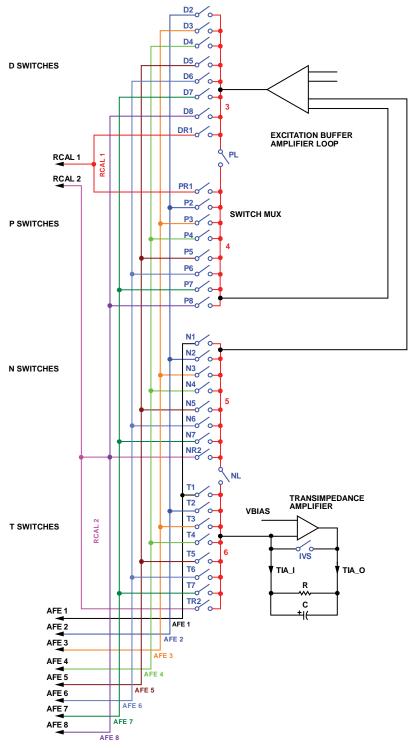

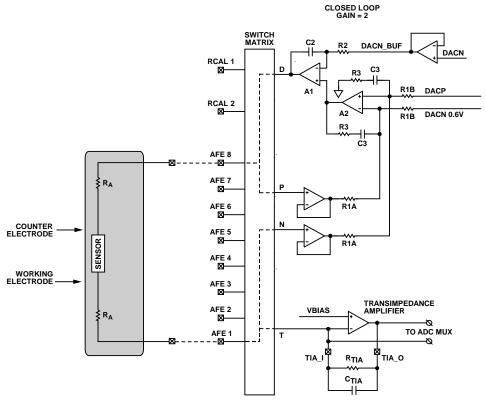

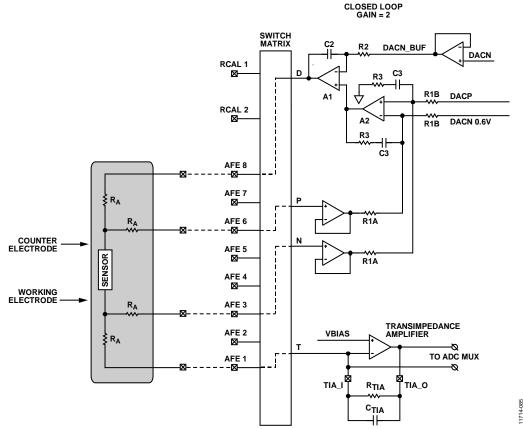

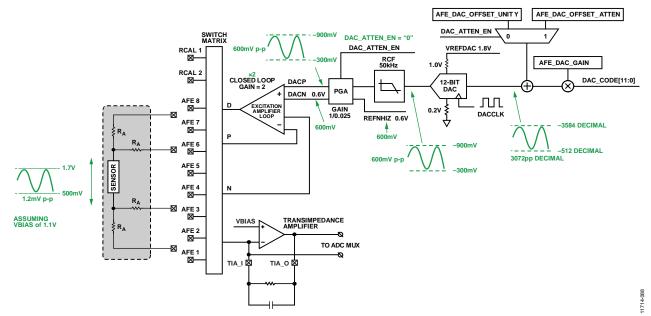

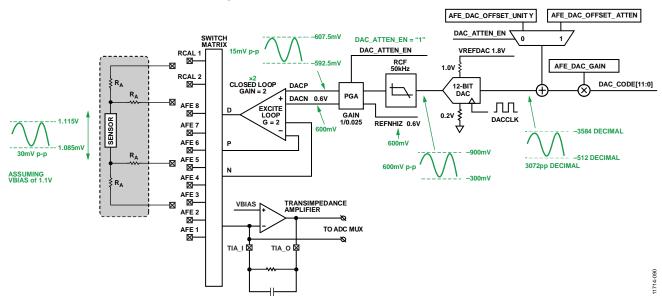

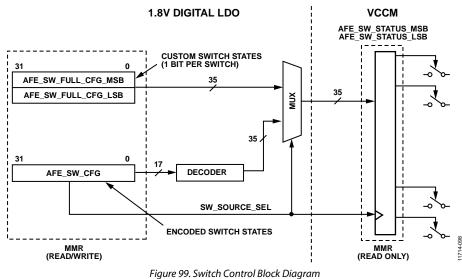

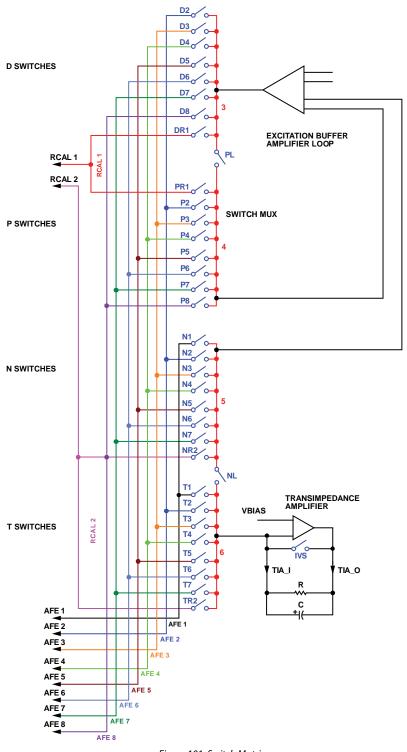

| AFE Excitation Loop                                                                               | 8 |

| Introduction                                                                                      | 8 |

| Switch Matrix                                                                                     | 9 |

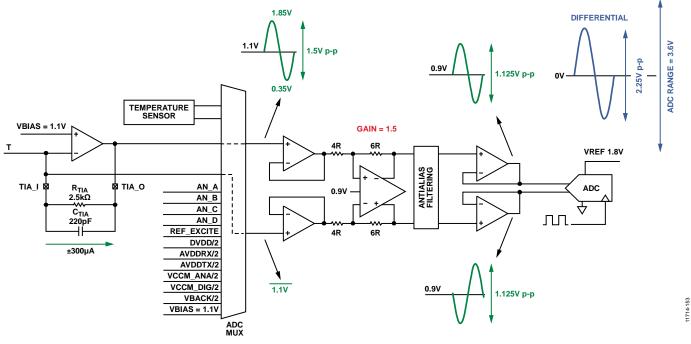

| Basic Loop Theory                                                                                 | ) |

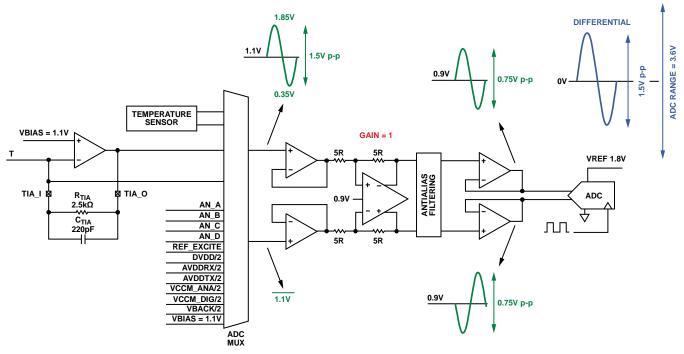

| AFE Signal Swings                                                                                 | 2 |

| Receive Stage                                                                                     | 3 |

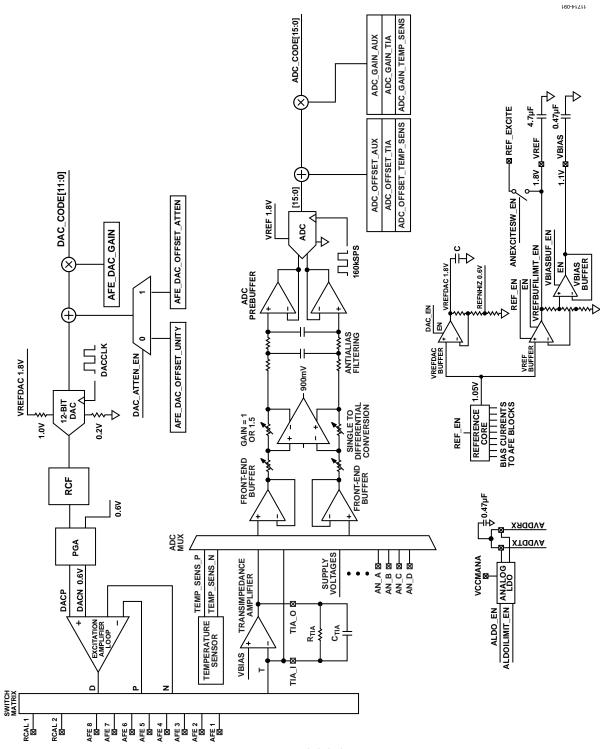

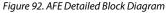

| Analog Front-End Interface                                                                        | 4 |

| Features                                                                                          | 4 |

| Module Architecture                                                                               | 5 |

| Operation                                                                                         | 7 |

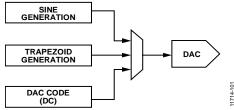

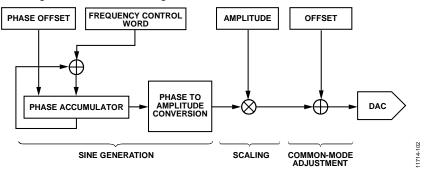

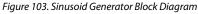

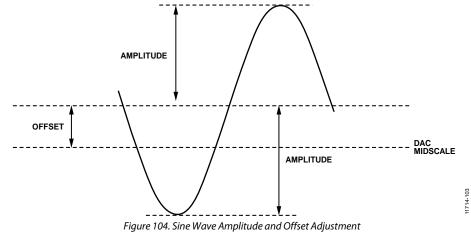

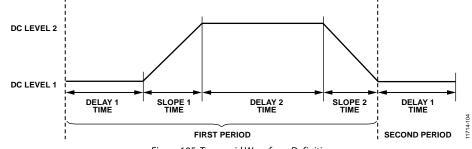

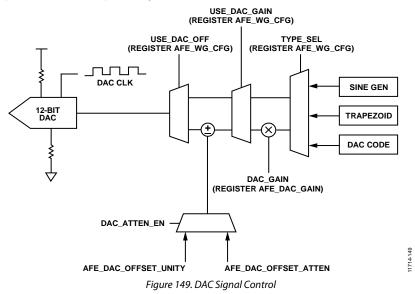

| Waveform Generator                                                                                | 5 |

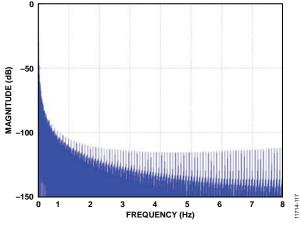

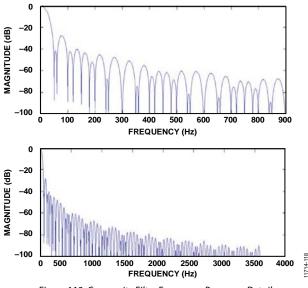

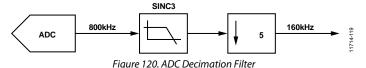

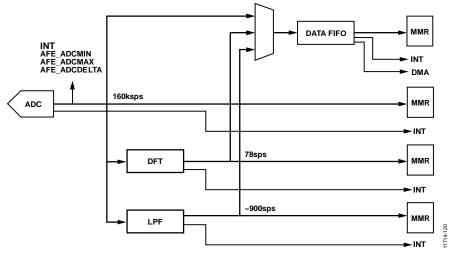

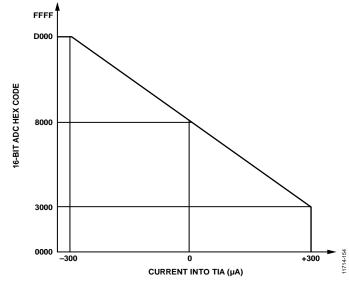

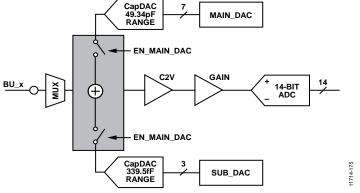

| ADC Receive Stage                                                                                 | 3 |

| AFE Memory Mapped Registers                                                                       | 5 |

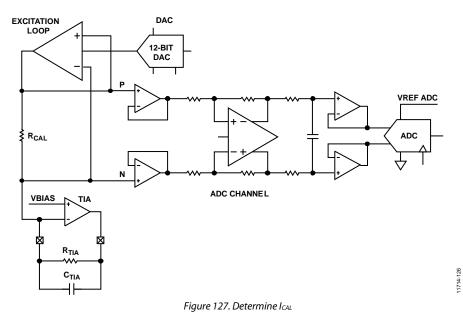

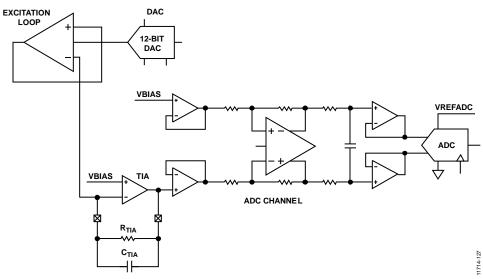

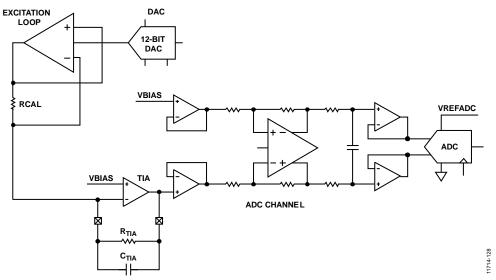

| No Factory Calibration                                                                            | 1 |

| Introduction                                                                                      | 1 |

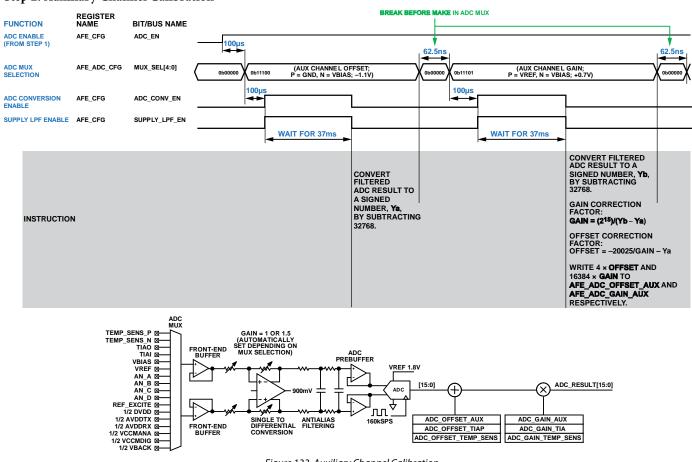

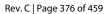

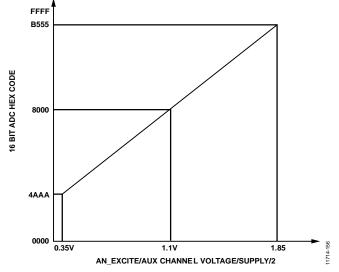

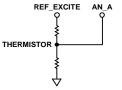

| Proposed Calibration Routine for Auxiliary Channel 36                                             | 1 |

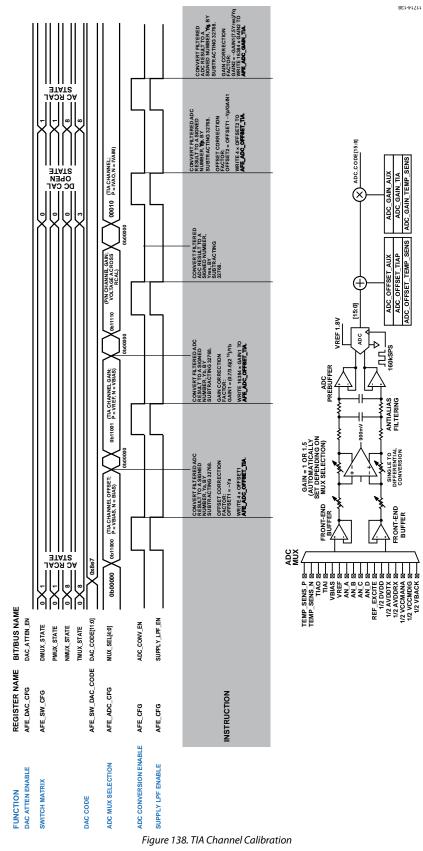

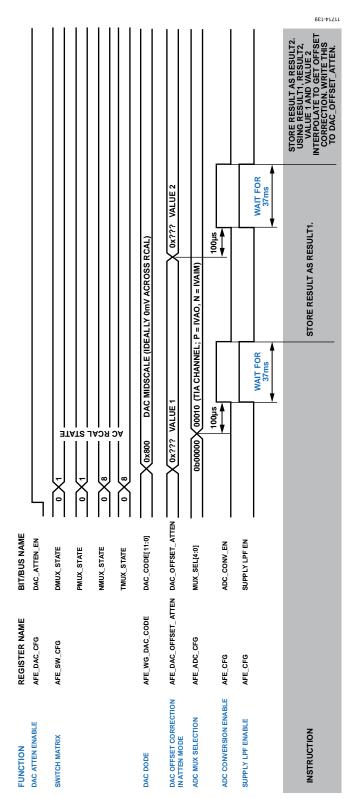

| Proposed Calibration Routine for the Current Measurement<br>Through TIA                           | 3 |

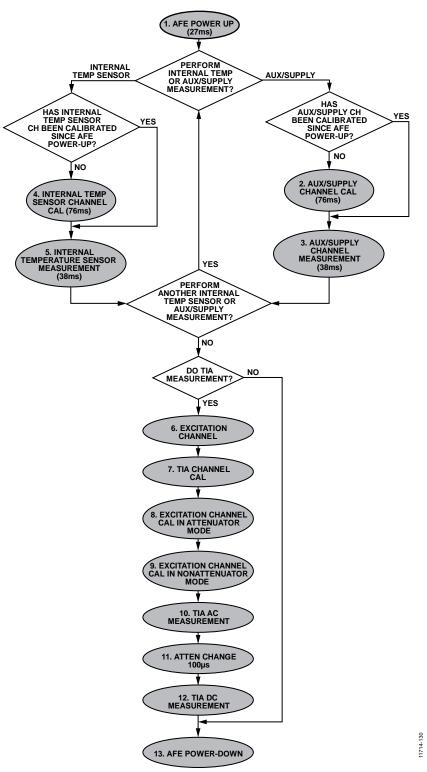

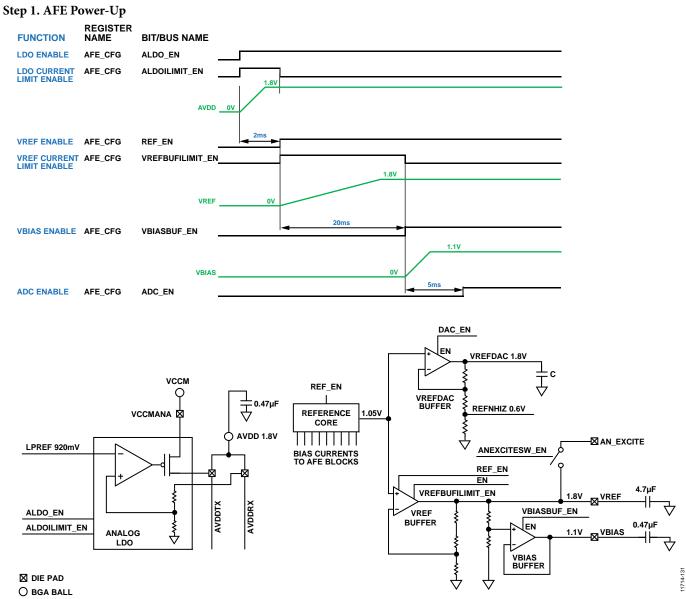

| No Factory Calibration Sequence                                                                   | 4 |

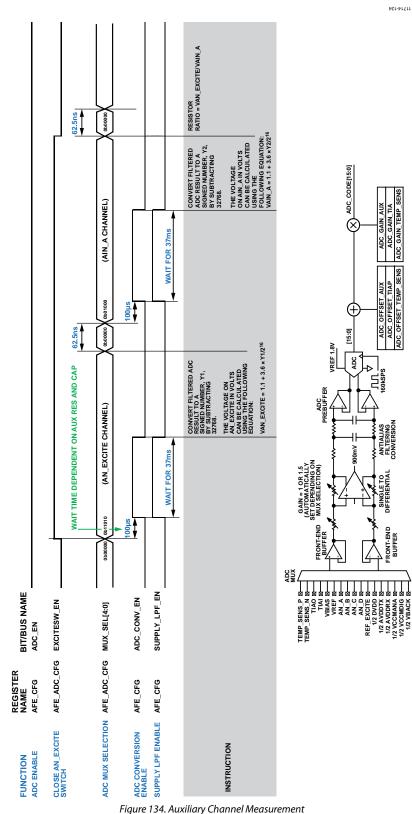

| Proposed Calibration Routine for Internal Temperature<br>Sensor on AFE Power-Up                   |   |

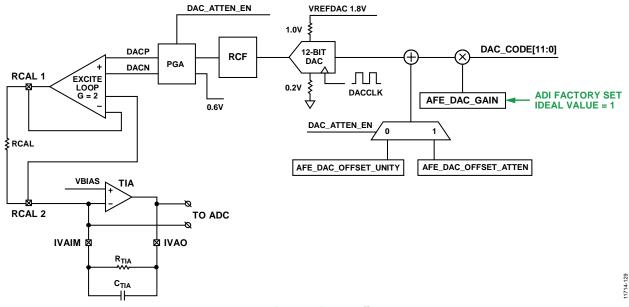

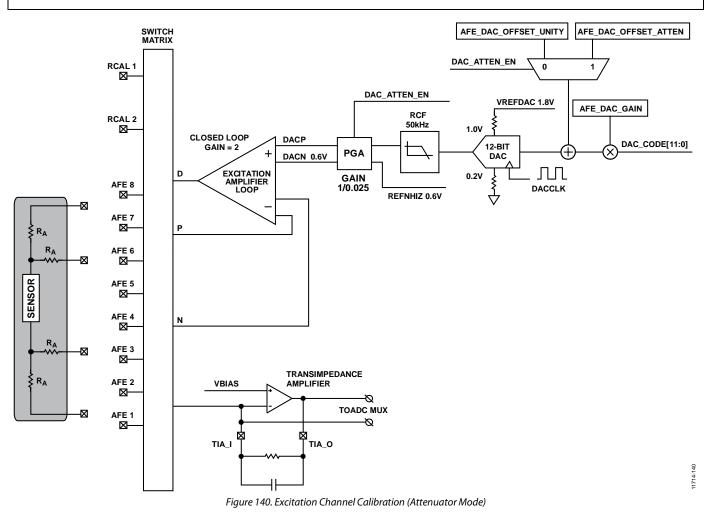

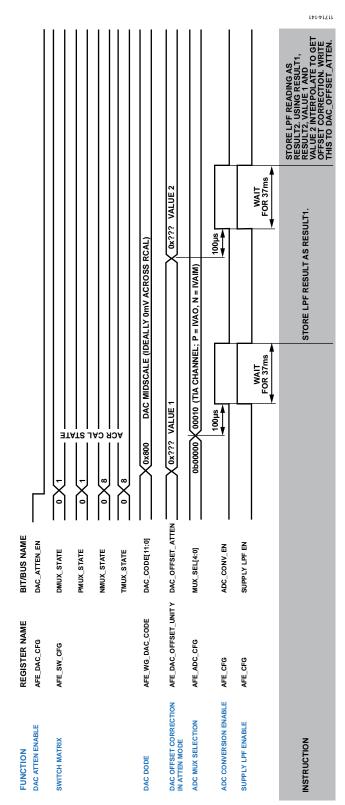

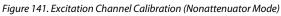

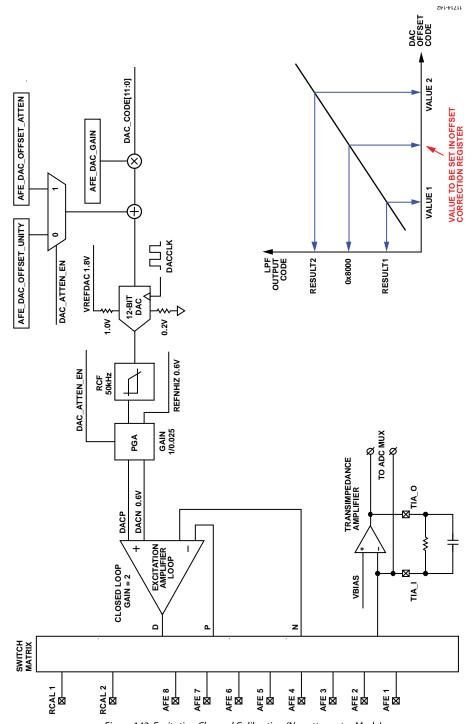

| Proposed Calibration Routine for Excitation Channel (DAC and Excitation Loop) on the AFE Power-Up | 0 |

| AFE Example Use Cases                                                                             | 3 |

## ADuCM350 Hardware Reference Manual

| Introduction                           |

|----------------------------------------|

| Example Use Case Flow Diagram          |

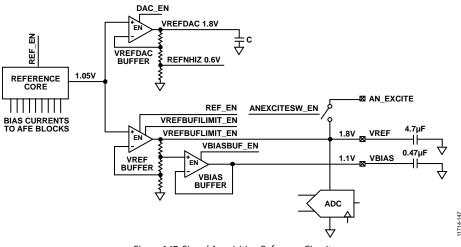

| Precision Voltage Reference and Bias   |

| Introduction                           |

| Precision Reference Requirements       |

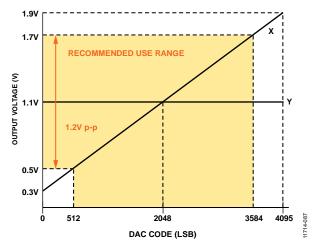

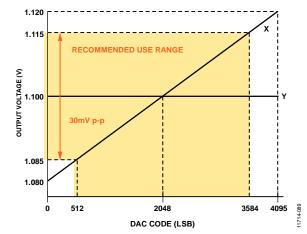

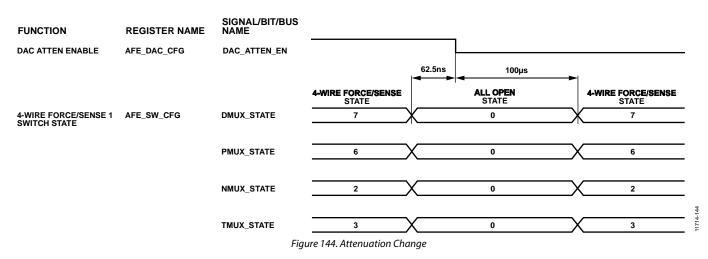

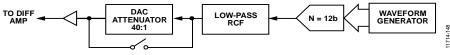

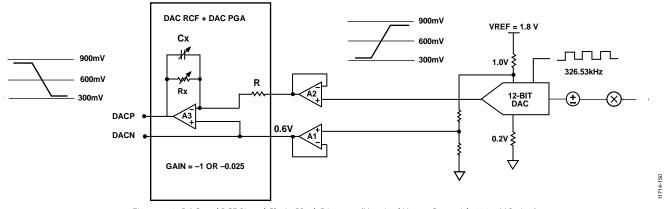

| DAC and Low-Pass RCF 391               |

| Introduction                           |

| DAC and Low-Pass RCF in Signal Chain   |

| DAC Attenuator 392                     |

| DAC Signal Generation Requirements 392 |

| LP RCF Operation                       |

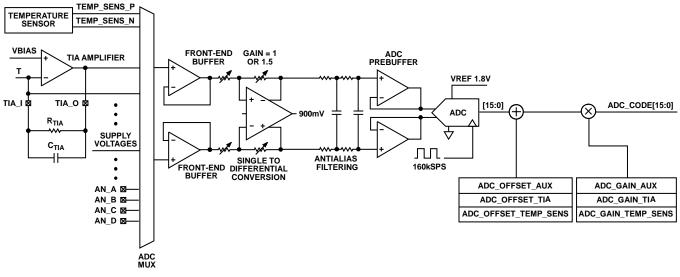

| ADC Channel 394                        |

| Introduction                           |

| ADC Channel Block Diagram 394          |

| Reference Dependence                   |

| ADC Multiplexer 395                    |

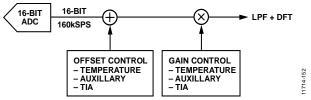

| ADC Calibration 396                    |

| ADC Measurement 396                    |

| ADC Registers                          |

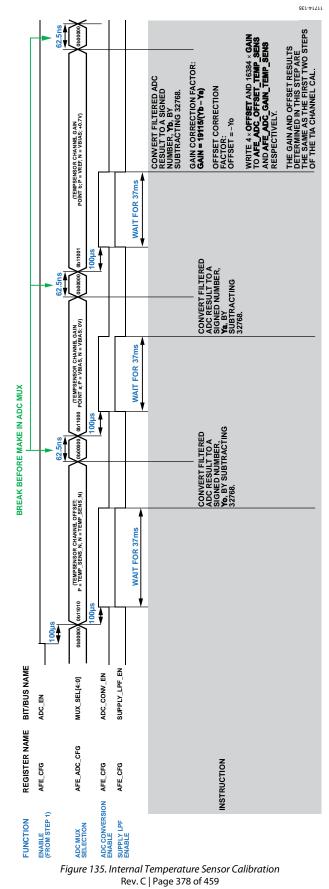

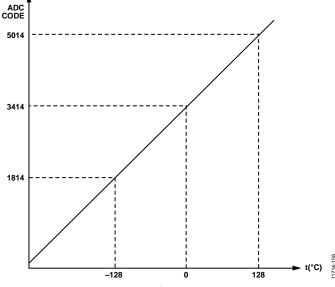

| Temperature Sensor Measurement 399     |

| Introduction                           |

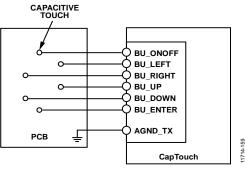

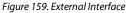

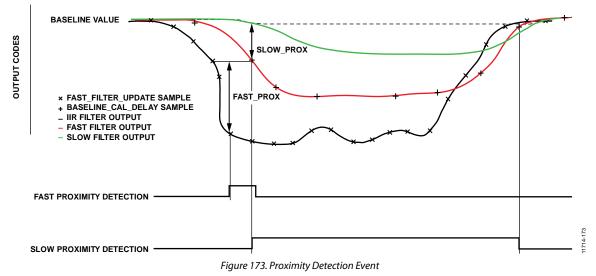

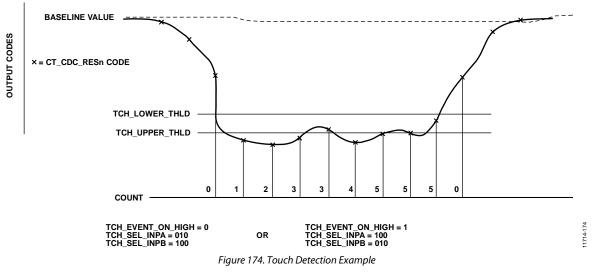

## Temperature Sensor Measurement Data Format......400 Temperature Sensor Gain and Offset Calibration ......400 Capacitive Touch Interface ......401 Introduction......401 Internal Block Diagram......401 Capacitive Touch Memory Mapped Registers ......414 Pins.....451 Introduction......451 Pin Configuration and Function Descriptions ......452 Digital Input/Output Pads ......456 Discrete Capacitor Requirements......456 RESETX......456 ESD Requirements......456

## **REVISION HISTORY**

| 5/2016—Rev. B to Rev. C                       |      |

|-----------------------------------------------|------|

| Changes to AFE Retention In Hibernate Section | .315 |

| Deleted Table 470; Renumbered Sequentially    | .315 |

### 9/2015—Rev. A to Rev. B

| Changes to Figure 1                                     | 1    |

|---------------------------------------------------------|------|

| Changes to System Features Section                      | 7    |

| Changes to Debug Protocol Options Section               | 13   |

| Changes to Trace Output Section                         | 14   |

| Changes to Clock Dividers Section                       | 17   |

| Changes to PLL Programming Section, Table 8, and Intern | rupt |

| Section                                                 | 18   |

| Changes to Sequence Section                             | 19   |

| Changes to Platform LF RC Oscillator Section            | 20   |

| Changes to Table 17                                     | 35   |

| Changes to Clock Select Section and Table 31            | 56   |

| Changes to Introduction Section                         | 82   |

| Changes to Table 102                                    | 88   |

| Changes to Figure 34                                    |      |

| Changes to Table 108                                    | 93   |

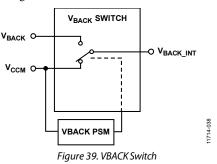

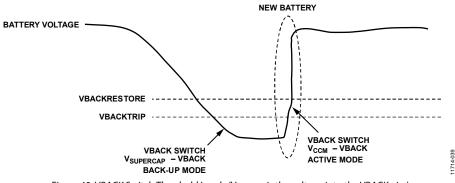

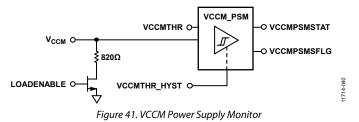

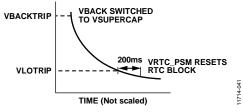

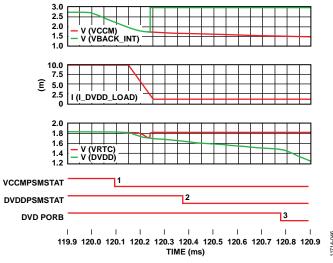

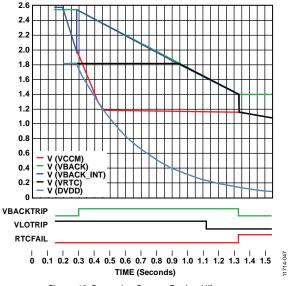

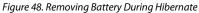

| Changes to Figure 39 and Figure 40 Caption              | 96   |

| Changes to Figure 44 and Figure 45                      | 99   |

| Changes to Figure 46 Caption and Figure 47              | 100  |

| Changes to Table 121                                    | 111  |

| Changes to Auto Request Section                             | 118   |

|-------------------------------------------------------------|-------|

| Changes to Address Calculation Section                      | 125   |

| Changes to Flash Integrity, Signature Feature Section       | 139   |

| Changes to Flash Integrity, Parity Feature for User Space 0 |       |

| Section and Parity Error Interrupt Section                  | 140   |

| Changes to RNG Oscillator Counter Section                   | 168   |

| Changes to Stall Issued to Control Transfer Section         | 177   |

| Changes to LPM Interrupt Enable Register Section            | 210   |

| Changes to Table 309                                        | 216   |

| Added Drive Strength Section                                | 222   |

| Changes to GPIO Port 1 Configuration Register Section       | 227   |

| Changes to GPIO Port 1 Drive Strength Select Register Sec   | ction |

| and GPIO Port 2 Configuration Register Section              | 230   |

| Changes to GPIO Port 3 Configuration Register Section       | 233   |

| Changes to GPIO Port 4 Configuration Register Section       | 237   |

| Changes to Functionality Section and Rx/Tx Data FIFOs       |       |

| Section                                                     | 240   |

| Changes to Figure 72                                        | 241   |

| Changes to Figure 73                                        | 242   |

| Changes to Power-Down Considerations Section                | 243   |

| Changes to Table 386                                        | 244   |

| Changes to Table 395 and Table 396                          |       |

| Changes to Table 407                                        | 252   |

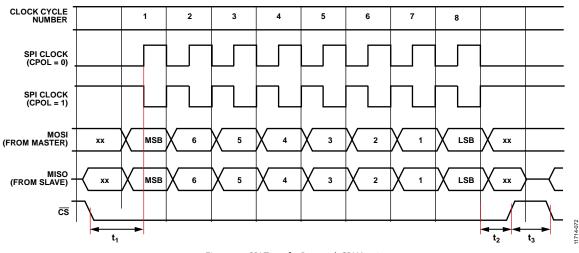

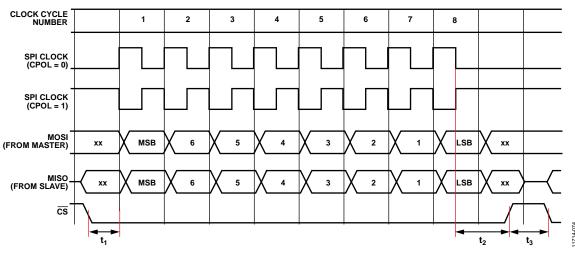

| Changes to SPI Transfer Initiation Section and Figure 74    | 254   |

## UG-587

# UG-587

| Changes to Figure 75                                       |

|------------------------------------------------------------|

| Changes to DMA Master Transmit Configuration Section 256   |

| Changes to DMA Master Receive Configuration Section 257    |

| Changes to LCD Charge Pump and External Capacitor          |

| Requirements Section and Figure 81                         |

| Added Table 450 Title                                      |

| Added Table 454 Title, Table 456 Title, and Figure 84;     |

| Renumbered Sequentially                                    |

| Changes to Basic Loop Theory Section                       |

| Added How to Use the TIA to Set the AFE Loop Common        |

| Mode Section                                               |

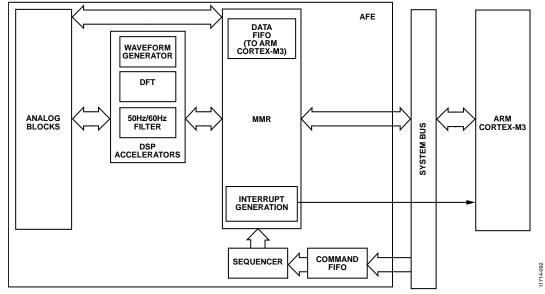

| Changes to Figure 97                                       |

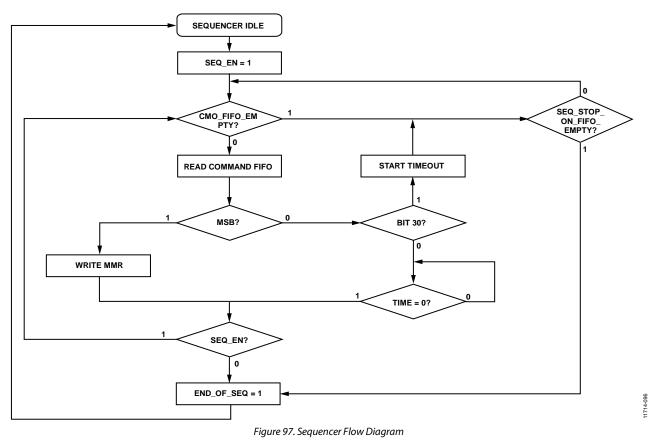

| Changes to Figure 98 Caption                               |

| Changes to Figure 100                                      |

| Added AFE Retention in Hibernate Section and Table 470 315 |

| Changes to Waveform Generator Section                      |

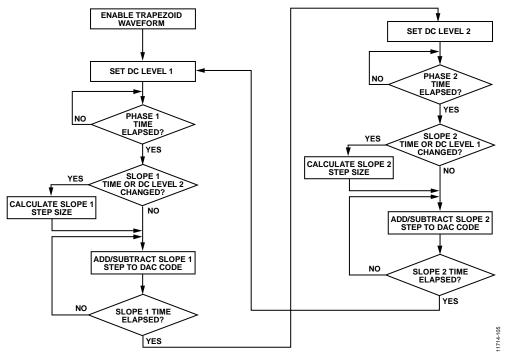

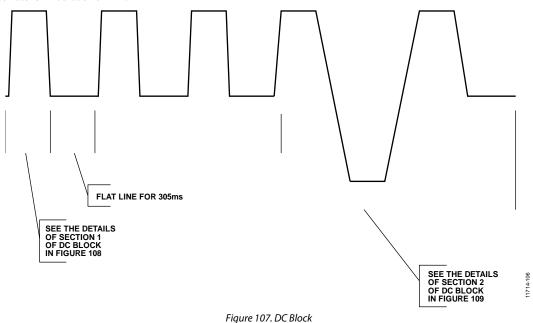

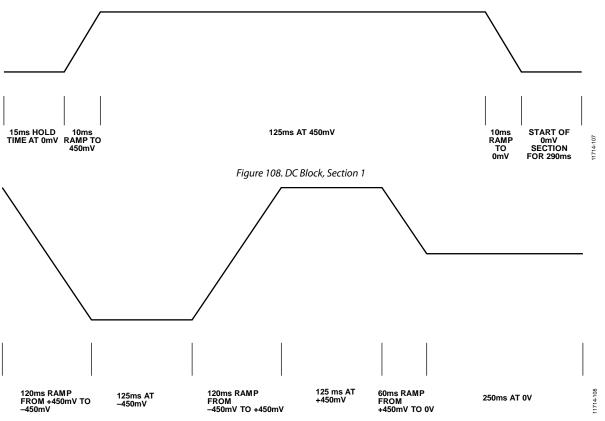

| Changes to Trapezoid Generator Section                     |

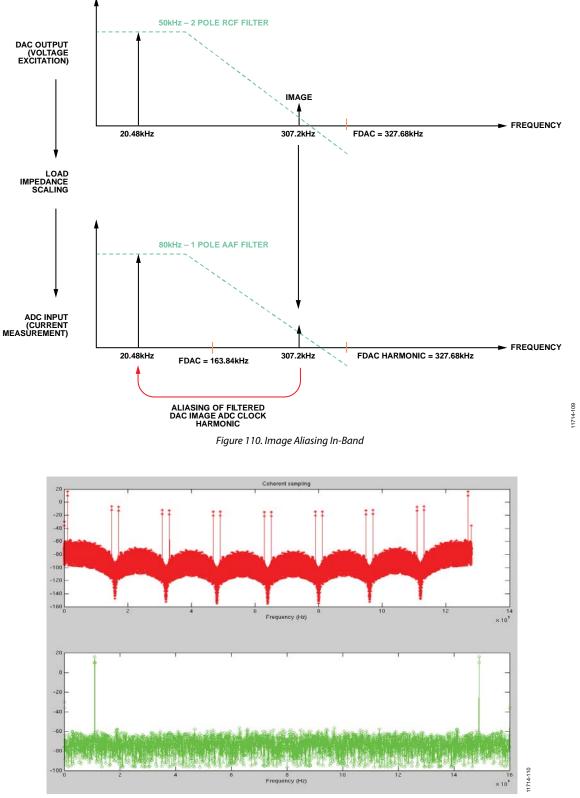

| Changes to Figure 113                                      |

|                                                            |

| Changes to Table 489                               | 341 |

|----------------------------------------------------|-----|

| Changes to No Factory Calibration Sequence Section | 364 |

| Changes to Figure 133                              | 376 |

| Deleted DAC Usage Cases Section                    | 407 |

| Changes to ADC Measurement Section                 | 396 |

| Changes to REF_EXCITE Functionality Section        | 398 |

| Changes to Temperature Sensor Usage Section        | 399 |

| Changes to Baseline Calibration Section            | 411 |

| Changes to Table 565                               | 415 |

| Changes to Table 566                               | 416 |

| Changes to Table 568 and Table 569                 | 418 |

| Changes to Table 571 and Table 582                 | 420 |

| Changes to Table 584 to Table 638                  | 424 |

| -                                                  |     |

|                                                    |     |

## 4/2014—Rev. 0 to Rev. A

| Changes to Bit 9 in Table | 13 |

|---------------------------|----|

|---------------------------|----|

3/2014—Revision 0: Initial Version

## INTRODUCTION

## SYSTEM FEATURES

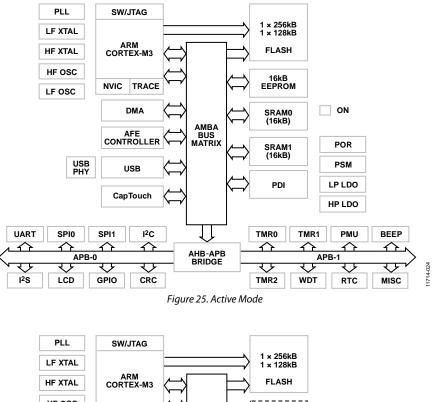

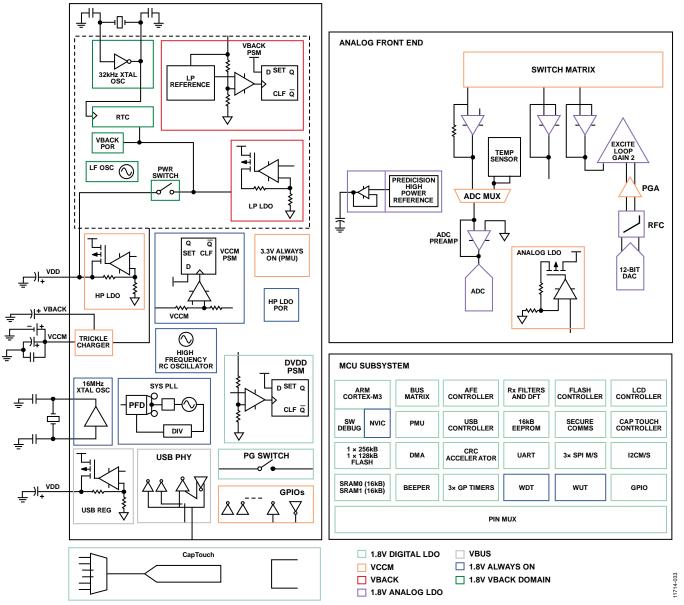

The ADuCM350 is an ultralow power, integrated mixed-signal metering solution that includes a microcontroller subsystem for processing, control, and connectivity. The microcontroller subsystem is based on an ARM Cortex<sup>™</sup>-M3 processor, a collection of digital peripherals, embedded SRAM and flash memory, and an analog subsystem that provides clocking, reset, and power management capabilities.

System features include the following:

- 16 MHz ARM Cortex-M3 processor

- 384 kB of embedded flash memory

- 32 kB system SRAM

- 16 kB EEPROM

- Integrated full speed USB 2.0 controller and PHY

- Power management unit (PMU)

- Multilayer advanced microcontroller bus architecture (AMBA) bus matrix

- Central direct memory access (DMA) controller

- I<sup>2</sup>S and beeper interfaces

- LCD controller functions

- Serial peripheral interface (SPI), I<sup>2</sup>C, and UART peripheral interfaces

- A real-time clock (RTC)

- An analog front-end (AFE) controller

- General-purpose, wake-up, and watchdog timers

- Programmable general-purpose inputs/outputs (GPIOs)

- A power-on reset (POR) feature and power supply monitor (PSM)

- A discrete Fourier transform (DFT) engine

- Receive filters

- Six-button CapTouch® interface

- 12-bit digital-to-analog converter (DAC)

- Temperature sensor

- Instrumentation amplifier control loop

- 16-bit analog-to-digital converter (ADC) performance

- High precision voltage reference

To support extremely low dynamic and standby power management, the ADuCM350 provides a collection of power modes and features, such as dynamic and software controlled clock gating and power gating.

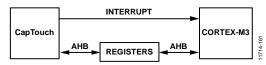

The AFE is connected to the microcontroller subsystem via an advanced high performance bus (AHB) slave interface on the AMBA bus matrix, as well as via the DMA and interrupt connections.

Note that throughout this hardware reference manual, multifunction pins (such as the TMS-SWDIO/P0.8 pin) are referred to either by the entire pin name or by a single function of the pin (for example, TMS-SWDIO) when only that function is relevant.

Full specifications on the ADuCM350 are available in the product data sheet, which should be consulted in conjunction with this reference manual when working with the device.

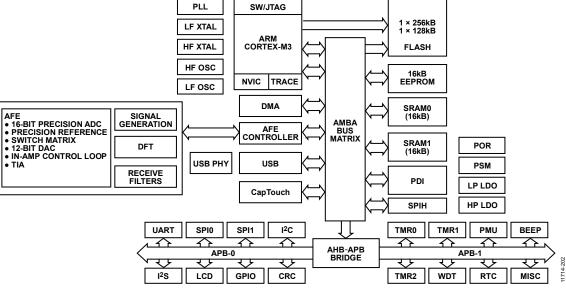

## SYSTEM BLOCK DIAGRAM

Figure 2. System Block Diagram

The ARM Cortex-M3 is a powerful 32-bit reduced instruction set computer (RISC) processor, offering up to 20 MIPS peak performance at 16 MHz. A central DMA controller is used to efficiently move data between peripherals and memory. On-chip 384 kB of nonvolatile flash memory, 16 kB EEPROM, and 32 kB of SRAM are also provided.

The device provides a range of flexible clocking features, allowing the system to operate from an internal RC oscillator, a crystal oscillator, or a phase-locked loop (PLL). A range of programmable clock divisions allows software to run the system at the minimum clock frequency required to save power.

The system also integrates a range of on-chip peripherals that can be configured via the microcontroller software for a given application. These peripherals include USB, UART, I<sup>2</sup>C, I<sup>2</sup>S, and SPI communication controllers, a GPIO port, general-purpose timers, a wake-up timer, and a system watchdog timer.

A PMU provides the system with four power modes that enable various levels of clock and power gating to minimize power consumption. In hibernate mode, activity on peripheral interfaces or events firing from the wake-up timer can wake up the device. Both software controlled and automatic clock gating are used to reduce dynamic power consumption, and power gating is also used to reduce standby current.

The AFE comprises a 12-bit DAC, an ADC with 16-bit performance, an instrumentation amplifier control loop, an integrated temperature sensor, a precision reference, and a pin switch matrix. The waveform generator DFT engine, receive filters, and AFE controller decouple the microcontroller core from the core analog control functions, which results in a highly tailored, power efficient measurement engine.

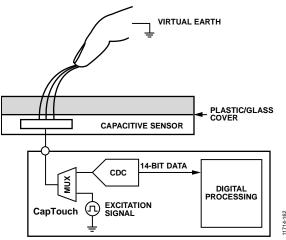

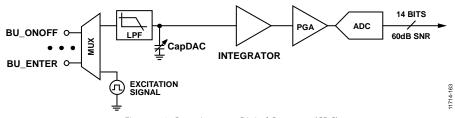

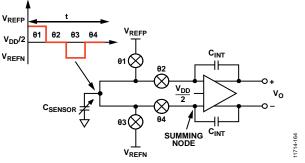

A six-button CapTouch interface allows the ADuCM350 to interface via a capacitive sensor using self capacitance measurements. The CapTouch interface supports a low power proximity mode; it also incorporates various noise reduction techniques, making it robust to environmental conditions.

## MEMORY ORGANIZATION

The ADuCM350 incorporates 384 kB of embedded flash memory for program code and nonvolatile data storage, 16 kB of EEPROM, and 32 kB of SRAM. The flash memory uses 2 kB of information space (not shown in the memory map), which includes a software kernel as well as manufacturing and test data.

Table 1 shows the ADuCM350 address map. Access to undefined address regions result in a memory management exception.

The SRAM and peripheral memory mapped registers are mapped to both the bit band region as well as a bit band alias region. The bit band alias region allows individual bits in memory to be accessed as words, allowing bit operations without having to write bit manipulation routines or additional language extensions.

The internal and external private peripheral bus regions provide access to M3 modules (if they are configured as being present), such as nested vectored interrupt controller (NVIC), instruction trace module (ITM), or flash patch and breakpoint (FPB) unit. For more information about these peripheral bus modules, consult the ARM Cortex-M3 Technical Reference Manual.

| First Address | Last Address | Memory Region                    |

|---------------|--------------|----------------------------------|

| 0x0000_0000   | 0x0005_FFFC  | 384 kB flash memory              |

| 0x2000_0000   | 0x2000_3FFF  | RAM Bank 0 (16 kB)               |

| 0x2004_0000   | 0x2004_3FFF  | RAM Bank 1 (16 kB)               |

| 0x2008_0000   | 0x2008_3FFF  | 16 kB EEPROM                     |

| 0x4000_0000   | 0x4000_001C  | General-Purpose Timer 0          |

| 0x4000_0400   | 0x4000_041C  | General-Purpose Timer 1          |

| 0x4000_0800   | 0x4000_081C  | General-Purpose Timer 2          |

| 0x4000_2400   | 0x4000_2404  | System power control             |

| 0x4000_2420   | 0x4000_2434  | External interrupts              |

| 0x4000_2440   | 0x4000_2440  | System reset                     |

| 0x4000_2500   | 0x4000_2540  | Wake-up timer                    |

| 0x4000_2580   | 0x4000_2598  | Watchdog timer                   |

| 0x4000_2600   | 0x4000_2618  | Real-time clock                  |

| 0x4000_3000   | 0x4000_3050  | I <sup>2</sup> C master/slave    |

| 0x4000_4000   | 0x4000_4018  | SPI0 master/slave                |

| 0x4000_4400   | 0x4000_4418  | SPI1 master/slave                |

| 0x4000_5000   | 0x4000_5030  | UART                             |

| 0x4000_5800   | 0x4000_5820  | I <sup>2</sup> S master/slave    |

| 0x4000_5C00   | 0x4000_5C08  | Beeper                           |

| 0x4000_6000   | 0x4000_6010  | Random bit generator             |

| 0x4000_8000   | 0x4000_804C  | LCD controller                   |

| 0x4001_0000   | 0x4001_0FFC  | DMA                              |

| 0x4001_8000   | 0x4001_807C  | Instruction flash controller     |

| 0x4001_C000   | 0x4001_C07C  | General-purpose flash controller |

| 0x4002_0000   | 0x4002_00B4  | GPIO                             |

| 0x4002_4000   | 0x4002_4018  | SPIH master/slave                |

| 0x4002_C000   | 0x4002_C032  | CRC engine                       |

| 0x4003_0000   | 0x4003_0048  | Parallel display interface       |

| 0x4008_0000   | 0x4008_0144  | AFE                              |

| 0x400A_0000   | 0x400A_03B4  | USB controller                   |

#### Table 1. ADuCM350 Memory Map

## **IDENTIFICATION REGISTERS**

The identification registers are described in Table 2.

| Address    | Name   | Description                            | Reset  | RW |

|------------|--------|----------------------------------------|--------|----|

| 0x40002020 | ADIID  | Analog Devices identification register | 0x4144 | R  |

| 0x40002024 | CHIPID | Chip identification register           | 0x0210 | R  |

#### Analog Devices Identification Register

The ADIID identification register is a 16-bit field that is present on all implementations of the Cortex-M3 low power platform. It is designed to be used by debuggers to confirm that the device that they are connected to via a serial wire is an implementation of the Cortex-M3 low power platform from Analog Devices. Debuggers can subsequently check the CHIPID identification register to identify the particular implementation used. The ADIID register has a default value of 0x4144, which does not vary between implementations. The ADIID register is located at Address 0x40002020. This address and value have been notified to tool vendors for device identification purposes.

#### **ADIID Register**

#### Address: 0x40002020, Reset: 0x4144, Name: ADIID

#### Table 3. Bit Descriptions for ADIID

| Bits   | Bit Name | Description                                            | Reset  | Access |

|--------|----------|--------------------------------------------------------|--------|--------|

| [15:0] | ID       | The fixed value of 0x4144 is present at this register. | 0x4144 | R      |

#### Chip Identification Register

The CHIPID identification register is a 16-bit field that is unique to an implementation of this Cortex-M3 low power platform. It can be used by code running on the Cortex-M3 to tailor its operation for that implementation. It is also designed for use by the serial wire debug tools to allow external debuggers to check the particular implementation of the Cortex-M3 low power platform and to tailor its operation for that implementation. The CHIPID register is located at Address 0x40002024.

#### **CHIPID Register**

#### Address: 0x40002024, Reset: 0x0210, Name: CHIPID

#### Table 4. Bit Descriptions for CHIPID

| Bits   | Bit Name | Description             | Reset | Access |

|--------|----------|-------------------------|-------|--------|

| [15:4] | PARTID   | Part identifier         | 0x21  | R      |

| [3:0]  | REVISION | Silicon revision number | 0x0   | R      |

## **ARM CORTEX-M3 CORE**

## FEATURES

The ADuCM350 contains an embedded ARM Cortex-M3 processor. The Cortex-M3 processor is an ARM processor for low cost embedded systems targeted at ultralow power processing requirements.

The ARM Cortex-M3 32-bit RISC processor features exceptional code efficiency, delivering the high performance expected from an ARM core in the memory footprint typically associated with 8-bit and 16-bit devices.

## **High Performance**

High performance features include the following:

- 1.25 DMIPS/MHz.

- Many instructions, including multiply are single cycle.

- Separate data and instruction buses allow simultaneous data and instruction accesses to be performed.

- Optimized for single cycle flash usage.

#### Low Power

Low power features include the following:

- Low standby current. The device includes a low power wake-up timer.

- Core implemented using advanced clock gating; therefore, only actively used logic consumes dynamic power.

- Power-saving mode support (sleeping and deep sleep). The design has separate clocks to allow unused parts of the core to be stopped.

#### Advanced Interrupt Handling

The NVIC supports up to 240 interrupts. The vectored interrupt feature greatly reduces interrupt latency because there is no need for software to determine which interrupt handler to serve. In addition, there is no need to have software to set up nested interrupt support.

The ARM Cortex-M3 processor automatically pushes registers onto the stack at interrupt entry and pops them back at interrupt exit. This reduces interrupt handling latency and allows interrupt handlers to be normal C functions.

### Dynamic Priority Control for Each Interrupt

Dynamic priority control for each interrupt includes the following:

- Latency reduction using late arrival interrupt acceptance and tail chain interrupt entry

- Immediate execution of a nonmaskable interrupt request for safety critical applications

#### System Features

System features include the following:

- Support for bit band operation, byte invariant big endian mode and unaligned data access.

- Advanced fault handling features include various exception types and fault status registers.

### **Debug Support**

Debug support includes the following:

- Serial wire and JTAG debug interfaces (SW-DP)

- Embedded trace Macrocell<sup>™</sup> provides high bandwidth instruction trace

- Flash patch and breakpoint (FPB) unit for implementing breakpoints

- Data watchpoint and trigger (DWT) unit for implementing watchpoints, trigger resources, and system profiling

## **FUNCTIONAL DESCRIPTION**

The ARM Cortex-M3 Technical Reference Manual describes all possible features of an ARM Cortex-M3 in detail.

As noted in the ARM Cortex-M3 Technical Reference Manual, several Cortex-M3 components are flexible in their implementation, such as SW/JTAG-DP, ETM, TPIU, ROM table, MPU, and NVIC.

### Serial Wire Debug (SW/JTAG-DP)

The device supports both the serial wire and JTAG interfaces via a common set of pins that multiplex both functions. See the ARM CoreSight<sup>™</sup> Components Technical Reference Manual for details on SWJ-DP.

# UG-587

## ROM Table

The default ROM table was implemented as described in the ARM Cortex-M3 Technical Reference Manual.

## NVIC

The ARM Cortex-M3 processor includes an interrupt controller, NVIC. It is closely coupled with the processor core and provides several features that include the following:

- Nested interrupt support

- Vectored interrupt support

- Dynamic priority changes support

- Interrupt masking

In addition, the NVIC also has a nonmaskable interrupt (NMI) input. The NVIC is implemented in the ADuCM350 and is described in more detail in the Nested Vectored Interrupt Controller section.

## Wake-Up Interrupt Controller (WIC)

Analog Devices has a modified WIC to provide the lowest power-down by removing the need for a clock to wake up the device. For more information, see the System Control Register section.

## DMA

The ADuCM350 implements the ARM  $\mu$ DMA. For more information, see the DMA Controller section.

For more information about the ARM Cortex-M3 processor core, see the following:

- ARM Cortex-M3 Technical Reference Manual

- ARM Cortex-M3 Devices Generic User Guide

- ARM Cortex-M3 Errata

## **DEBUG INTERFACE**

## INTRODUCTION

The ARM Cortex-M3 processor (R2P1) on the ADuCM350 supports two types of debug host interfaces, a 4-wire JTAG debug (JTAG) interface and a 2-wire serial wire debug (SWD) interface. To make efficient use of the package pins, the serial wire interface shares its pins with the JTAG interface.

### Table 5. Serial Wire and JTAG Pins

| CSPBGA Bump Location | Package Pin | JTAG | Serial Wire    |

|----------------------|-------------|------|----------------|

| H1                   | TMS-SWDIO   | TMS  | SWDIO          |

| H2                   | TCK-SWCLK   | TCK  | SWCLK          |

| J2                   | TDI         | TDI  | Not applicable |

| J1                   | TDO-SWO     | TDO  | Not applicable |

## **DEBUG PROTOCOL OPTIONS**

The two protocols, JTAG (IEEE 1149.1 Standard Test Access Port) and serial wire debug, are supported on the ADuCM350 for debug. Upon a power-on reset, the JTAG debug interface is selected by default. The user has the ability to switch between the SWD and JTAG by sending a specific sequence of 16 bits on the TMS-SWDIO pin. See the ARM Debug Interface v5 supplemental document for more details about this switching.

## INTERFACE ACCESS

The debug interface signals are selected by default on the pins. The GPIO pins can be assigned alternate function using the GPXCON port configuration registers. Care must be taken when selecting an alternate function because the debug interface is then not available to the user. In addition, the user must consider the state of DBG (FEECON1 Flash Control 1 register). If DBG is disabled, the debug of user code is prevented. Ensure that GPIO configuration, as well as enabling the debug interface, are part of the code debug strategy.

## **DEBUG FEATURES SUPPORTED**

The processor contains several system debug components that facilitate low cost debug, trace and profiling, breakpoints, watchpoints, and code patching, the details of which can be obtained from the ARM Cortex-M3 Technical Reference Manual.

The supported system debug components are as follows:

- Flash patch and breakpoint (FPB) unit to implement breakpoints and code patches.

- Data watchpoint and trace (DWT) unit to implement watchpoints, trigger resources, and system profiling.

- Instrumentation trace macrocell (ITM) for application driven trace source that supports printf style debugging.

- Embedded trace macrocell (ETM) for instruction trace. This is an optional feature that may be supported.

The details and programming model for all of these features can be obtained from the ARM Cortex-M3 Technical Reference Manual.

# EMBEDDED TRACE

## FEATURES

The ADuCM350 incorporates the complete embedded trace of the ARM Cortex-M3 processor features to maximize the code analysis, system profiling, and debugging capabilities. Data tracing, watchpoints, and various system profiling features are available from the data watchpoint and trace (DWT) unit. The instrumentation trace module (ITM) provides application-driven trace source that supports printf style debugging and generates system diagnostic information. The embedded trace macrocell (ETM) provides real-time instruction trace information.

## **TRACE IMPLEMENTATION**

The ADuCM350 implements the ARM ETM architecture v3.5. See the ARM Embedded Trace Macrocell Architecture Specification for detailed architecture and usage information.

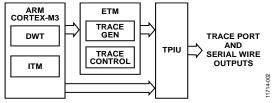

Figure 3. Embedded Trace Block Diagram

The DWT provides a selection of debugging features and contains four comparators that can each be programmed to be a hardware watchpoint, an ETM trigger, a PC sampler event trigger, or a data address sampler event trigger. It also includes several counters that can be used to record how many clock cycles or instructions various functions take to complete. The DWT is described in detail in the ARM Cortex-M3 Technical Reference Manual.

The ITM allows application software the ability to write console messages and output these messages as trace data, generating trace information as packets to the trace port interface unit (TPIU). It also generates and inserts timestamps into the trace stream to help the debugger to identify event ordering. The ITM is described in both the ARM Cortex-M3 Technical Reference Manual as well as the ARMv7-M Architectural Reference Manual.

The ETM generates instruction trace packets to be transmitted from the trace port interface at the core clock rate to the off chip debugger. Both 16-bit and 32-bit thumb instructions can be traced. Tracing is enabled and disabled by using four compare registers in the DWT, by using up to two external trace sources inside the Cortex-M3, or by using dedicated start and stop bits controlled by the DWT. A 24-byte hardware first in, first out (FIFO) is used to buffer instruction packets.

The TPIU provides the interface between the ITM and ETM modules, formatting and serializing the packets before transmission out the trace port to an off chip trace port analyzer.

## **TRACE OUTPUT**

There are two formats of trace data output that are supported on the ADuCM350. One format is the 4-pin parallel trace, which uses the standard 4-pin version of the Cortex-M3 trace port interface unit.

For reduced pin count, the single pin trace output option is also available. Serial wire trace output that is multiplexed with TDO-SWO pin can be used to output trace data. However, this is not recommended to be used along with ETM. More details can be obtained from the ARM Cortex-M3 Technical Reference Manual.

## SYSTEM CLOCKS

## **FEATURES**

The ADuCM350 integrates two on-chip oscillators and the circuitry for two external crystals:

- LFOSC is a 32 kHz internal oscillator.

- HFOSC is a 16 MHz internal oscillator.

- LFXTAL is a 32 kHz external crystal oscillator.

- HFXTAL is an 8 MHz or 16 MHz external crystal oscillator.

A duty cycle correction (DCC) block is used to balance the output clock from HFXTAL to 50% duty cycle for the system. It is enabled together with HFXTAL.

Two on-chip PLLs are also available: the system PLL (SPLL) and the USB PLL (UPLL). Both PLLs can use either the HFOSC or the HFXTAL as an input clock.

The high frequency oscillators (HFOSC and HFXTAL), along with the output of the SPLL, can be used to generate the root clock.

The root clock is divided into many internal clocks:

- FCLK clocks the NVIC, which includes SYSTICK of the Cortex-M3 core.

- HCLK\_CORE clocks the Cortex-M3 core.

- HCLK\_BUS clocks the advanced high performance bus (AHB) peripherals.

- PCLK clocks the advanced peripheral bus (APB) peripherals.

- Each peripheral has a UCLK that is synchronous to the PCLK for its internal operation (with the exception of SPIH, which is synchronous to HCLK). Each UCLK can be gated individually.

- USBCTLCLK clocks the USB control logic and must be ≥30 MHz when the USB is connected.

- ACLK clocks the AFE and must be 16 MHz when the analog front end is actively working.

- AFE\_ADC\_CLK clocks the ADC inside AFE and must be 16 MHz when the analog front end is actively working. AFE\_ADC\_CLK shares the same control bits as ACLK: CLKCON5[7] (ACLKOFF).

- HCLK\_CT clocks all the digital in the CapTouch block except for the ADC controller and the self timer. HCLK\_CT shares the same control bit in Power Mode 2: CLKCON5[8] (CTCLKOFF). This clock must be 16 MHz when the CapTouch is actively working.

- CTCLK clocks the ADC controller only, and generates clocks and control signals for the CapTouch analogue section and must be 16 MHz when the CapTouch is actively working.

A USBPHYCLK for clocking the USB PHY is also available and must use a 60 MHz clock when the USB is connected; however, its source is the direct output of the UPLL, not the root clock.

The 32 kHz clock (LF\_CLK) is generated from either LFXTAL or LFOSC to drive certain blocks, including the watchdog timer, LCD, beeper, and CapTouch self timer. The wake-up timer and general-purpose timers have their own multiplexers to select their clock source. The RTC always works from LFXTAL.

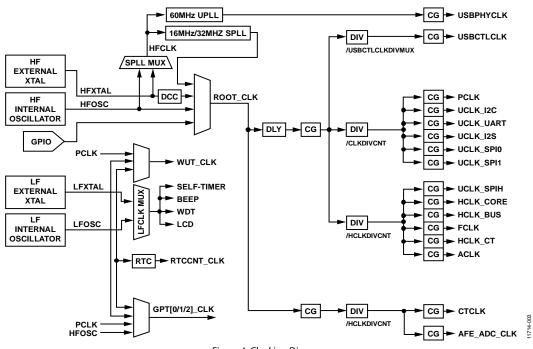

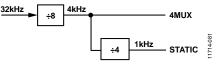

Figure 4 shows a diagram of all the clocks available and includes the clock gates for power management.

Note that the delay block (DLY) is used to offset the clock phase of the digital system away from the phase of the AFE and CapTouch ADCs to ensure that the ADCs can sample correctly and that the digital system is as quiet as possible.

Figure 4. Clocking Diagram

## **OPERATION**

At power-up, the core executes from a 1 MHz system clock. The user is then given control to program a clocking scheme appropriate for the application, which is done by setting values in the clocking registers.

### **Clock Muxes**

There are three clock source multiplexers, as shown in Figure 4: the root clock mux (ROOT\_CLK), the low frequency clock mux (LFCLK Mux) band, and the SPLL input mux (SPLL Mux). These clock source multiplexers are controlled using memory mapped registers.

The dashed multiplexers for the wake-up timer and general-purpose timers are controlled via registers within the corresponding blocks. See the Wake-Up Timer (WUT) section and the General-Purpose Timers section for details.

In general, ensure that the desired clock input is available and stable for the clock selection made for the clock mux. Otherwise, situations where the system can be locked out of a stable clock can arise. Registers used to program the clock settings are on the HCLK\_BUS domain.

The ADuCM350 provides the facility to observe the various clocks used in the system on an external pin. The GPIO Pin P1.7 is used for this purpose. This feature is available as Function 4 on the P1.7 pin. To observe this clock on Pin P1.7, select the function using the GP1CON register (GP1CON[15:14] = 0x3). The clock source that appears on Pin P1.7 is selected in the miscellaneous clock settings register (CLKCON0[7:4]).

As an example, to view the LFXTAL clock on the P1.7 pin, the following needs to be selected:

- The GPIO clock source needs to be selected in Bits[1:0] of the CLKCON0 register.

- The LFXTAL must be enabled in Bit 8 of the CLKCON0 register.

| Register | Bit(s)                                 | Selection                                                                                                     |  |

|----------|----------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| CLKCON0  | [1:0]                                  | 00: HFOSC                                                                                                     |  |

|          |                                        | I: HFXTAL                                                                                                     |  |

|          |                                        | 10: SPLL                                                                                                      |  |

|          |                                        | 11: GPIO (Pin P0.11 test purposes only)                                                                       |  |

| CLKCON0  | 11                                     | 0: HFOSC                                                                                                      |  |

|          |                                        | 1: HFXTAL                                                                                                     |  |

| CLKCON0  | 8                                      | 0: LFOSC                                                                                                      |  |

|          |                                        | 1: LFXTAL                                                                                                     |  |

| T2CON    | [10:9]                                 | Controlled by the wake-up timer                                                                               |  |

| GPTXCON  | [6:5]                                  | Controlled by General-Purpose Timer 0/General-Purpose Timer 1/General-Purpose Timer 2                         |  |

|          | CLKCON0<br>CLKCON0<br>CLKCON0<br>T2CON | CLKCON0         [1:0]           CLKCON0         11           CLKCON0         8           T2CON         [10:9] |  |

#### Table 6. Clock Muxing

| Clocks         | Register | Bit(s) | Selection              |

|----------------|----------|--------|------------------------|

| GPIO Out Clock | CLKCON0  | [7:4]  | 0000: ROOT_CLK         |

|                |          |        | 0001: LF_CLK           |

|                |          |        | 0010: CTCLK            |

|                |          |        | 0011: HCLK_BUS         |

|                |          |        | 0100: HCLK_CORE        |

|                |          |        | 0101: PCLK             |

|                |          |        | 0110: USBCTRLCLK       |

|                |          |        | 0111: USBPHYCLK        |

|                |          |        | 1000: GPT0_CLK         |

|                |          |        | 1001: GPT1_CLK         |

|                |          |        | 1010: GPT2_CLK         |

|                |          |        | 1011:WUT_CLK           |

|                |          |        | 1100: RTCCNT_CLK       |

|                |          |        | 1100 to 1111: not used |

## **Clock Dividers**

Four programmable clock dividers are available to generate the clocks in the system. A clock divider integer divides the input clock down to a new clock. The division range is from 1 to 32. Division selection can be made on the fly. The output remains glitch free and stretches the high time, never creating a high time shorter than the pre or post value of the clock period.

Three of the clock dividers use the root clock as an input and generate the core and peripheral synchronized clocks. The clock dividers are cascaded in such a way that each stage initially releases its divided clock in a sequence. The last stage informs all other stages that its divided clock is ready to be output. The effect of this cascading is that divided clocks are released synchronously when new divider values are programmed. Initial edges of each clock are mutually aligned.

An additional independent divider is available to generate the CapTouch clock. It uses the same divider counter as HCLKDIVCNT because CTCLK always has the frequency of HCLKs. Table 7 summarizes the inputs and outputs of each clock divider along with the register bits to program each clock divider.

| Divider | Input Clock | Output Clocks                                       | Bits in the CLKCON1 Register |

|---------|-------------|-----------------------------------------------------|------------------------------|

| 0       | Root clock  | HCLK_CORE, HCLK_BUS, FCLK, ACLK, CTCLK, AFE_ADC_CLK | HCLKDIVCNT                   |

| 1       | Root clock  | PCLK, all peripheral UCLKs                          | PCLKDIVCNT                   |

| 2       | Root clock  | USBCTLCLK                                           | USBCTLCLKDIVMUX              |

## Table 7. Clock Dividers Sources and Outputs

Divider 2 does not have a programmable divide value. Its divide value can be either HCLKDIVCNT or half of HCLKDIVCNT. When the USBCTLCLKDIVMUX bit is set to 0, USBCTLCLK equals HCLK. When the bit is set to 1, the USBCTLCLK is twice the frequency of HCLK. Note that for the 2× relationships to hold between HCLK and USBCTLCLK, the HCLK divider must be an even number. If the LSB of the divider is 1, it truncates when the divider value is shifted right by 1. For example, if the HCLK divider is 7 and USBCTLCLKDIVMUX is 1, the USBCTLCLK divider is 3, making the illegal relationship between the two clocks 7/3 instead of 2/1.

Only certain divider ratios are legal between PCLK and HCLK. Specifically, the following rules must be respected:

- The frequency of PCLK must always be smaller or equal to the frequency of HCLK.

- The ratio of the dividers must be an integer.

- PCLK must be the same speed as HCLK before going into hibernate mode.

In general, clock division can be changed on the fly during normal operation; however, one exception is a USB transfer. Do not distribute clocks during a USB transfer; therefore, do not program a new divider until USB tasks are completed.

## **Clock Gating**

In the case of certain clocks, clocks can be individually gated depending on the power mode or register settings. For more information about clock gating and power modes, refer to the Power Management Unit section.

The clock gates of the peripheral UCLKs are user controllable in certain power modes. Register CLKCON5 can be programmed to turn off certain clocks, depending on user application. Set the respective bits to 1 in the CLKCON5 register to disable clock gates.

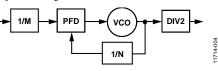

## PLL Programming

Figure 5 shows the abstract PLL structure for both SPLL and UPLL. It has the multiplier coefficient, N, and divider coefficient, M, to decide the output clock ratio of N/M. There is an optional DIV2 built in the PLL to either divide down the PLL output clock by 2 or directly output it.

The PLL should always switch away from ROOT\_CLK when changing any coefficients or clock sources.

When the reference clock for the phase frequency detector (PFD) has a 4 MHz input, the PLL has its best phase margin. Therefore, it is recommended that for a 16 MHz crystal clock input, configure M as 4, and for an 8 MHz crystal clock input, configure M as 2.

Figure 5. PLL Diagram

Table 8 shows the example and recommended settings for SPLL to output a 16 MHz or a 32 MHz clock and for UPLL to output a 60 MHz clock.

| PLL  | Input Clock (MHz) | М | Ν  | DIV2 | Output Clock (MHz) |

|------|-------------------|---|----|------|--------------------|

| SPLL | 16                | 4 | 8  | 0    | 32                 |

| SPLL | 16                | 4 | 16 | 1    | 32                 |

| SPLL | 8                 | 2 | 8  | 0    | 32                 |

| SPLL | 8                 | 2 | 16 | 1    | 32                 |

| SPLL | 8                 | 2 | 4  | 0    | 16                 |

| SPLL | 8                 | 2 | 8  | 1    | 16                 |

| UPLL | 16                | 4 | 15 | 0    | 60                 |

| UPLL | 8                 | 2 | 15 | 0    | 60                 |

#### Table 8. PLL Recommended Setting

The PLL settings can be programmed using the CLKCON3 and CLKCON4 registers. Both of these registers contain the same control bits for the two separate PLLs (SPLL and UPLL). To enable SPLL or UPLL, the SPLLEN or UPLLEN bit must be set, respectively. The SPLL or UPLL N multiplier can be set using the SPLLNSEL or UPLLNSEL bits, respectively. The M divider can also be set using the SPLLMSEL or UPLLMSEL bits according to the following:

- 00: divide by 1.

- 01: divide by 2.

- 10: divide by 4.

- 11: reserved.

An optional division by 2 of the input SPLL and UPLL clock can be programmed by setting the SPLLDIV2 and UPLLDIV2 bits, respectively.

### Interrupts

Either PLL can interrupt the core when it locks or when it loses its lock. To enable the SPLL and UPLL interrupts, the SPLLIE and UPLLIE bits in the CLKCON3 and CLKCON4 registers must be set. The SPLLUNLOCK and UPLLUNLOCK bits in the CLKSTAT0 register indicate that the SPLL and UPLL unlock events have happened. The SPLLLOCK and UPLLLOCK bits in the CLKSTAT0 register indicate that a SPLL or UPLL lock event has happened. Both of these bits are used to interrupt the core when PLL interrupts are enabled. Both bits are sticky and must write a 1 to be cleared. These bits are different from the SPLLSTATUS and UPLLSTATUS bits in CLKSTAT0, which simply mirrors the value of the SPLL or UPLL lock signal (1 = locked, 0 = unlocked).

Regarding the SPLL or UPLL lock event, while it is fine to use the lock detect status bits to determine when the PLL clock is safe to use and locked initially, it is not advised to use the unlock sticky bits as a means to declare the PLL clocks are unsuitable; that is, it is not a reliable indicator that the PLL has lost lock. The reason for this is that the SPLL and UPLL sensitivity threshold is too low and causes the detect function to be too sensitive for conditions related to environment, application, or device. To start using the system PLL, the following sequence of events is recommended. The example multiplies a 16 MHz crystal input to 32 MHz via the SPLL and uses it as the root clock. The HCLK is set to 16 MHz and the PCLK to 4 MHz.

- 1. Enable PLL interrupts by setting SPLLIE in CLKCON3 to 0x1.

- 2. Set the PLL input to the external high frequency (HF) crystal (XTAL oscillator). Set PLLMUX in CLKCON0 to 0x1.

- 3. Enable the external crystal (HFXTAL oscillator). Set HFXTALEN in OSCCTRL to 0x1.

- 4. Set the clock dividers consistent with the intended system clock rates. For example, assuming a PLL output of 32 MHz sets the HCLK to 16 MHz and the PCLK to 4 MHz, set PCLKDIVCNT in CLKCON1 to 0x08 and HCLKDIVCNT in CLKCON1 to 0x02.

- 5. Set up the PLL M and N values and enable the PLL. Set SPLLEN in CLKCON3 to 0x1, SPLLMSEL in CLKCON3 to 0x2, and SPLLNSEL in CLKCON3 to 0x08.

- 6. Wait for the PLL interrupt indicating that the PLL has locked. Optionally, also check that the crystal is stable at this stage, even though the PLL should not lock if the crystal is not stable.

- 7. Clear the PLL interrupt and select PLL as the system clock source. Set SPLLLOCK in CLKSTAT0 to 0x1 and CLKMUX in CLKCON0 to 0x2.

The USB PLL is programmed following a simpler but similar sequence of events. Step 2 and Step 7 are not required because there is only one input to the UPLL (the HF crystal), and it is the only possible source to the USB PHY clock.

For Step 4, the UPLL requires precharging of the loop to prevent the VCO from turning off. This is a two-part process as follows:

- 1. Set divider ratio to precharge loop for a duration of 200 μs. Set the UPLLMSEL value = 0x2 and the UPLLNSEL value = 0x3F.

- 2. Set divider ratio to desired UPLL frequency. Set the UPLLMSEL value = 0x2 and the UPLLNSEL value = 0x0F.

#### **Crystal Programming**

The crystals are disabled by default and can be programmed using the OSCCTRL register. The crystals can be enabled by setting the HFXTALEN or LFXTALEN bits. The stable signal status bits are also mirrored in this register.

Note the following:

- Before issuing a SYSRESETREQ, allowing the Cortex-M3 to assert a reset request signal to the system reset generator, the HFOSCEN (OSCCTRL bit 1) must be set to ensure that all system components reset properly. This is independent of the root clock mux and SPLL clock mux settings.

- When disabling the external LFXTAL, the LFXTAKEN bit must be written to twice with a delay of at least two low frequency clock periods between write commands.

#### Interrupts

Each crystal can interrupt the core when its output clock becomes stable. The interrupts are enabled by setting the HFXTALIE and LFXTALIE bits in the CLKCON0 register. Register CLKSTAT0 contains the stable information pertaining to both crystals. The HFXTALSTATUS and LFXTALSTATUS bits in the CLKSTAT0 register contain the current state of the stable signals of the crystals. The HFXTALOK or LFXTALOK bits in the CLKSTAT0 register are set when an event is detected on the stable signals of the crystals. The HFXTALOK/HFXTALNOK and LFXTALOK/LFXTALNOK bits are sticky and must be cleared by writing a 1 to them. The HFXTALNOK and LFXTALNOK bits are not continuous XTAL monitors and are only set as a confirmation that the corresponding XTAL has been properly disabled.

#### PLL Clock Protection

In the event that the clock source to the PLL is lost, the PLL maintains operation at a reduced output frequency. This behavior allows PLL interrupt sources such as SPLLUNLOCK and UPLLUNLOCK (CLKSTAT0 Bit 6 and Bit 2) to be serviced and enables the appropriate action to be taken by the core. This feature protects the core from an indefinite stall due to broken or shorted leads of the XTAL circuit.

### **Oscillator Programming**

Both the internal oscillators are enabled by default. Before issuing a SYSRESETREQ, allowing the Cortex-M3 to assert a reset request signal to the system reset generator, the HFOSCEN (OSCCTRL Bit 1) must be set. This ensures that all system components are reset properly. This is independent of the root clock mux and SPLL clock mux settings.

Enabling the HFOSC is done by using the HFOSCEN bit in the OSCCTRL register. Note that before stopping the HFOSC internal oscillator, the HFXTAL must be running the system. Otherwise, the device locks because its clock has been stopped by the user without possibility of recovery. Similarly, the LFOSC internal oscillator can be enabled with the LFOSCEN bit in the OSCCTRL register. Peripherals driven with a 32 kHz clock must be switched over to the LFXTAL external crystal oscillator before the LFOSC internal oscillator is disabled.

## INTERNAL RC AND EXTERNAL XTAL OSCILLATORS

## Platform HF RC Oscillator

The 16 MHz high frequency oscillator is enabled by the HFOSCEN bit. The RC oscillator is calibrated to  $\pm 5\%$ .

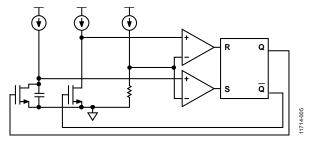

Figure 6. HF RC Oscillator Block Diagram

## Platform LF RC Oscillator

The 32.768 kHz low frequency RC oscillator is enabled by the LFOSCEN bit. The RC oscillator is calibrated to ±20% and is in the 3 V domain.

Figure 7. LF RC Oscillator Block Diagram

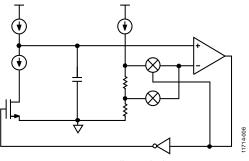

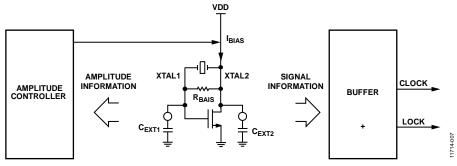

## Platform HF XTAL Oscillator

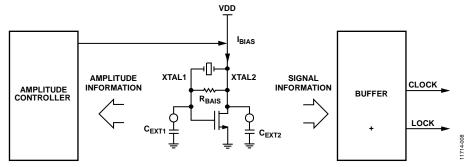

The HF XTAL oscillator is the accurate clock source of the system, with a frequency of 16 MHz. It is used as an input for the system/USB PLL or as a direct clock source for the respective digital clock requirements and is in the 1.8 V domain.

Figure 8. HF XTAL Block Diagram

## Platform LF XTAL Oscillator

The LF XTAL oscillator is the clock source for the RTC. It is used to keep the time of the system. It provides a 32.768 kHz output clock with an external load of 15 pF.

Once the oscillator is enabled, it remains always on, even in hibernate and supercapacitor mode.

Figure 9. LF XTAL Block Diagram

## **EXAMPLE USE CASES**

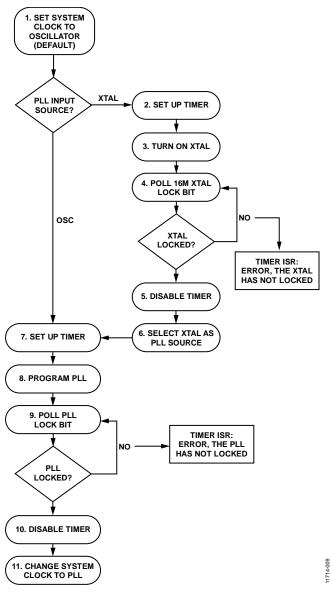

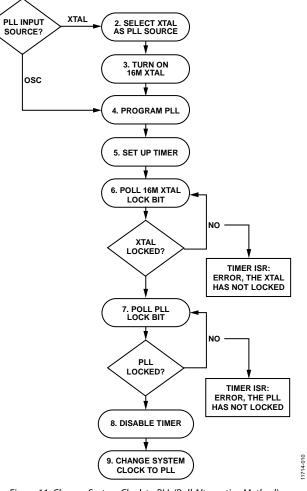

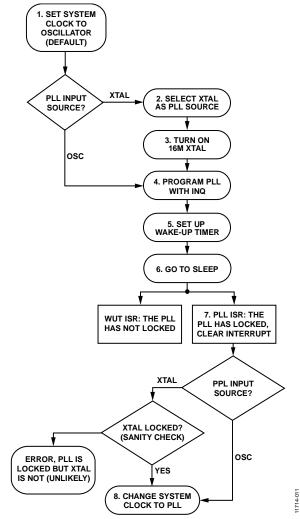

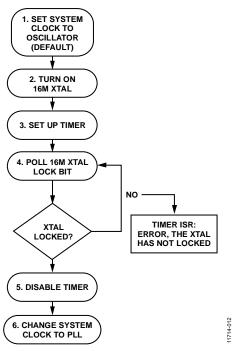

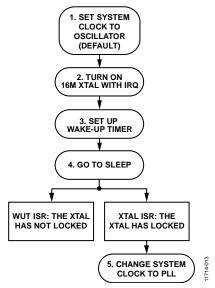

The following flow diagrams highlight the sequence of events required to set the system/USB clocks.

## Set System Clock to PLL Input Source

The following three timing diagrams show the sequence of events to change the system clock from being based on an internal RC oscillator to being based on a PLL input source.

Figure 10. Change System Clock to PLL (Poll Method)

1. SET SYSTEM CLOCK TO OSCILLATOR (DEFAULT)

Figure 11. Change System Clock to PLL (Poll Alternative Method)

Rev. C | Page 23 of 459

UG-587

Figure 12. Change System Clock to PLL (IRQ Method)

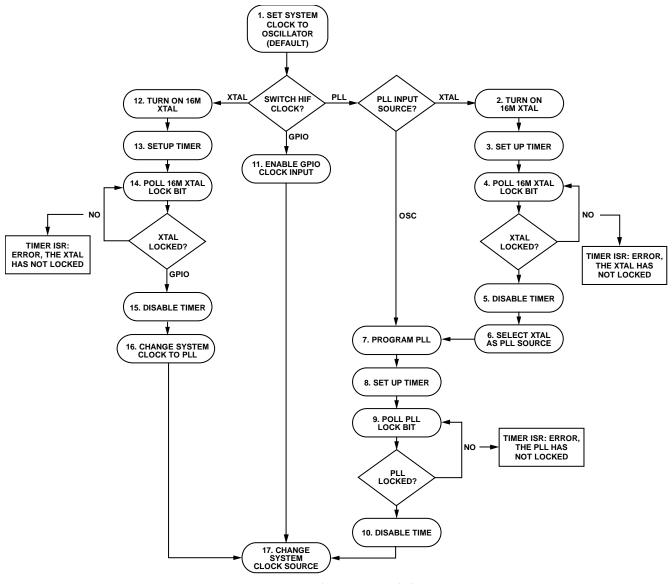

## Set System Clock to XTAL

The following two timing diagrams show the sequence of events to change the system clock from being based on an internal RC oscillator to being based on an XTAL source.

Figure 13. Change System Clock to XTAL (Poll Method)

Figure 14. Change System Clock to XTAL (IRQ Method)

11714-014

## Changing System Clock Source

The following diagram shows the sequence to change the system clock source from being based on an RC oscillator to being based on one of the following: an XTAL, a GPIO input, or a PLL input source.

Figure 15. Changing System Clock

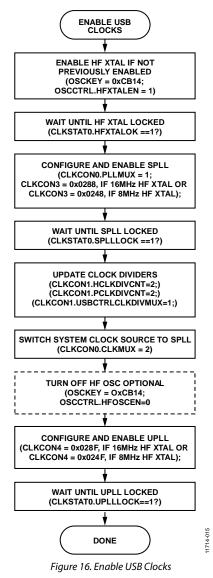

## **Clocking Control for USB**

The USB controller requires a 32 MHz controller clock and a 60 MHz PHY clock, while the rest of the system can run with a 16 MHz clock. This section describes when to change the clocks.

The control of USB clocks relates to clock dividers (CLKCON1), HF XTAL and PLLs (OSCKEY, OSCCTRL, CLKCON3, CLKCON4, CLKSTAT0), and system clock multiplexer (CLKCON0).

Whenever the USB connection or resume activity is detected, switch the system clock to a 32 MHz clock and enable the UPLL. When USB is disconnected or suspended, the system clock can be switched back to 16 MHz and both the SPLL and UPLL can be disabled. For LPM sleep state, due to its fast (50 µs to 1.2 ms) wake-up requirement, the HF XTAL must remain active but UPLL can be turned off (UPLL needs about 35 µs to restart, whereas HF XTAL needs ~10 ms to restart).

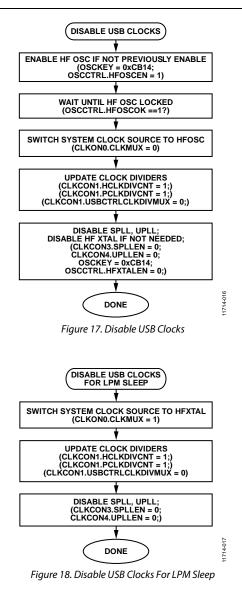

Figure 16, Figure 17, and Figure 18 describe how to enable and disable the USB clocks. The USB clocks must be enabled when the USB is in use and disabled when the USB is not in use.

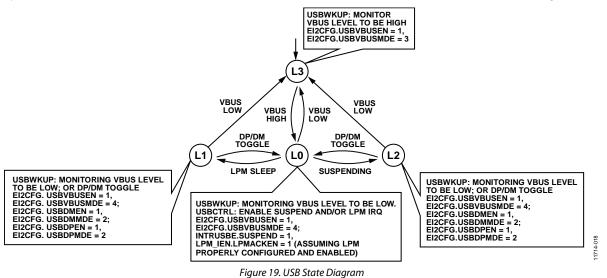

The following diagram describes how the USB transits between its working states: L0 (on), L1 (sleep), L2 (suspend), and L3 (off).

To detect the activity of the USB when transiting between these states, the USBWKUP logic is required. The USBWKUP logic has level or edge detection of USBVBUS, DP, and DM lines as controlled in EI2CFG and generates an interrupt at Position Number 36 (see Table 114) if enabled by EI2CFG.USBVBUSEN, EI2CFG.USBDMEN, and/or EI2CFG.USBDPEN. The detection events are saved at Register USBWKSTAT.

## L3

Initially, the USB controller enters the L3 state by default and does not require the USBCTLCLK or USBPHYCLK. It can only transit to the L0 state if the USB controller is enabled and connected. To detect the USB connection while in the L3 state, configure the USBWKUP block to monitor the USBVBUS line for a high state. When USBVBUS is detected as high, call the enable USB clocks task to have the 32 MHz USBCTLCLK and the 60 MHz USBPHYCLK so that the USB can transit from L3 to L0.

## L0

The active USB state requires a 32 MHz USBCTLCLK and a 60 MHz USBPHYCLK to work properly for USB transactions. When in the L0 state, the USB controller can transit to

- The L2 state if the USB data bus (DP and DM) idles for more than 3 ms.

- The L1 state if the LPM command is acknowledged.

- The L3 state if a disconnection occurs.

Enable the USBWKUP logic to monitor the VBUS level so that it can generate an interrupt when VBUS is low, which occurs when the USB is disconnected. In such a case, the disable USB clocks task can be called to use 16 MHz for rest logic to save power.

In addition, the USB controller should enable the suspend interrupt so that it can notify the user when the USB data bus idles for more than 3 ms. If this occurs, the disable USB clocks task can be called to use 16 MHz for rest logic to save power.

If LPM is supported and properly configured, enable the LPM interrupt so that the LPM command can be acknowledged. If this occurs, the disable USB clocks for LPM task can be called to use the 16 MHz HF XTAL for rest logic to save power. (The user may have to leave the PLL running if a very short resume period is required.)

## L2

The suspend state does not need any USBCTLCLK or USBPHYCLK clock. The L2 state can transit to L3 when a disconnection occurs or to L0 if USB bus activity is detected.

To detect a disconnection, configure the USBWKUP logic to monitor when the VBUS line becomes low. If this occurs, the disable USB clocks task can be called to use 16 MHz for rest system if the clocks are not disabled yet. (Although the internal logic of the USB controller might appear to remain in suspend mode, this does not adversely affect the operation of the device. The internal logic of the USB controller is updated after a new connection is detected.)

To detect resume or reset activity, configure the USBWKUP logic to monitor DP (MD is redundant and might not have to be enabled). If this occurs, call the enable USB clocks task to have the 32 MHz USBCTLCLK and the 60 MHz USBPHYCLK so that the USB can transit to the L0 state.

## L1

The LPM sleep state is defined for fast sleep (instead of 3 ms idling) and fast resume in the USB 2.0 standard. This state does not require low power as a compromise. The HF XTAL must remain active; otherwise, it cannot resume operation quickly enough. Optionally, UPLL can be disabled if the restart period is adequate. Otherwise, the L1 state is similar to the L2 state; therefore, the USB controller can transit to the L3 state when a disconnection occurs or to the L0 state if USB bus activity is detected. The USBWKUP logic should be configured the same as it is for the L2 state; the response is also the same as it is for the L2 state. If the UPLL is disabled, the user must enable the system clock to 32 MHz before reenabling the UPLL to ensure that pulses from the USBPHYCLK domain to the USBCTLCLK domain can be detected.

Table 9 lists the mentioned interrupts and corresponding interrupt service routine (ISR).

| USB Event                                                | USB Wake-Up Monitoring or Interrupt                                 | Service for USB Wake-Up Interrupt                      |

|----------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|

| New Connection (L3 to L0)                                | USBWKUP logic detecting VBUSVAILD for<br>high (EI2CFG[15:12] = 0xB) | Enable USB clocks                                      |

| Disconnection (L0, L1, or L2 to L3)                      | USBWKUP logic detecting VBUSVAILD for<br>low (EI2CFG[15:12] = 0xC)  | Disable USB clocks or disable USB clocks for LPM sleep |

| Suspend (L0 to L2)                                       | INTRUSB:SUSPEND in USB controller                                   | Disable USB clocks                                     |

| LPM Sleeping (L0 to L1)                                  | LPM_IRQ:LPMACK in USB controller                                    | Disable USB clocks for LPM sleep                       |

| USB Resume (L1 or L2 to L0)                              | USBWKUP logic detecting DP toggle<br>(El2CFG[7:4] = 0xA)            | Enable USB clocks                                      |

| USB Reset (When L1 or L2;<br>No Clocking Action When L0) | USBWKUP logic detecting DP toggle<br>(EI2CFG[7:4] = 0xA)            | Enable USB clocks                                      |

### Table 9. Interrupts for USB Clock Control

## SYSTEM CLOCKS MEMORY MAPPED REGISTERS

## System Clocks Register Map

#### Table 10. Clocking Register Summary

| Address    | Name            | Description                  | Reset   | RW |

|------------|-----------------|------------------------------|---------|----|

| 0x4000240C | OSCKEY          | Key protection for OSCCTRL   | 0x0000  | RW |

| 0x40002410 | OSCCTRL         | Oscillator control           | 0x0003  | RW |

| 0x40028000 | CLKCON0         | Miscellaneous clock settings | 0x0000  | RW |

| 0x40028004 | CLKCON1         | Clock dividers               | 0x1010  | RW |

| 0x40028008 | RESERVED        | Reserved                     | 0x0000  | R  |

| 0x4002800C | CLKCON3         | System PLL                   | 0x0088  | RW |

| 0x40028010 | CLKCON4         | USB PLL                      | 0x008F  | RW |

| 0x40028014 | CLKCON5         | User clock gating control    | 0x0180  | RW |

| 0x40028018 | <b>CLKSTATO</b> | Clocking status              | 0x0000  | RW |

| 0x4002801C | RESERVED        | Reserved                     | Unknown | R  |

| 0x40028810 | RESERVED        | Reserved                     | 0x0000  | R  |

| 0x40028814 | RESERVED        | Reserved                     | 0x0000  | R  |

| 0x40028818 | RESERVED        | Reserved                     | Unknown | R  |

| 0x4002881C | RESERVED        | Reserved                     | Unknown | R  |

| 0x40028820 | RESERVED        | Reserved                     | Unknown | R  |

| 0x40028824 | RESERVED        | Reserved                     | 0x0000  | R  |

| 0x40028828 | RESERVED        | Reserved                     | 0x0000  | R  |

| 0x4002882C | RESERVED        | Reserved                     | Unknown | R  |

| 0x4002883C | RESERVED        | Reserved                     | 0x0000  | R  |

#### Key Protection for OSCCTRL Register

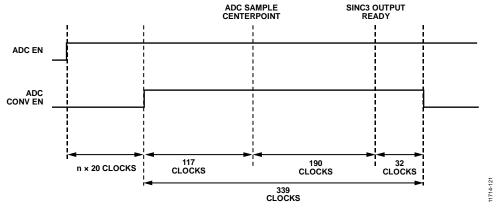

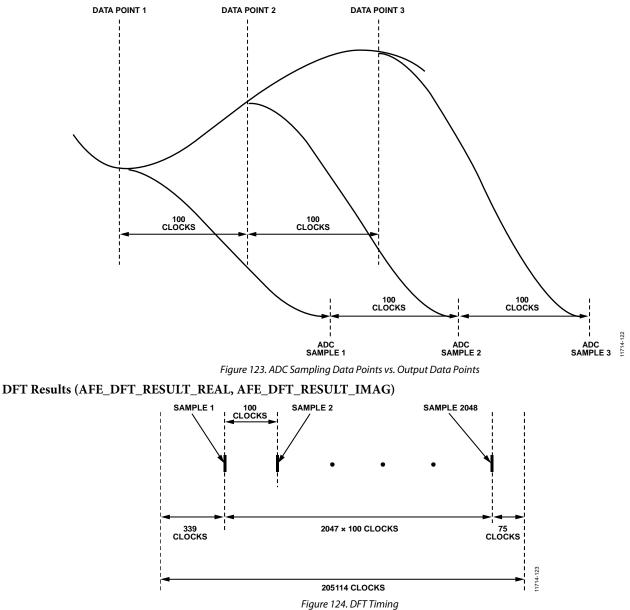

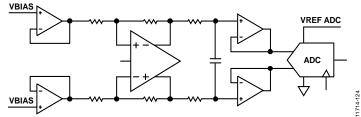

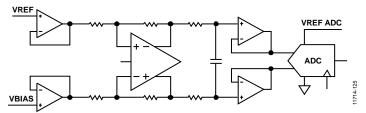

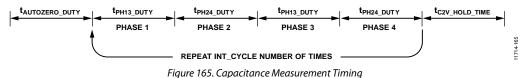

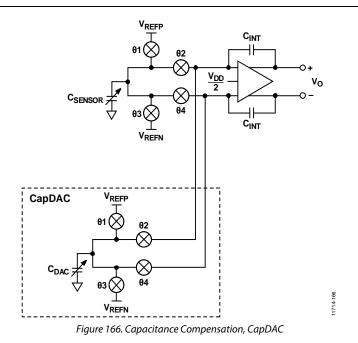

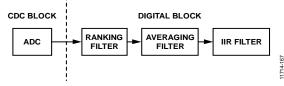

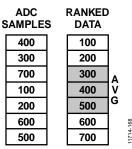

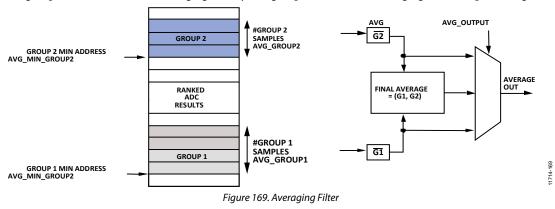

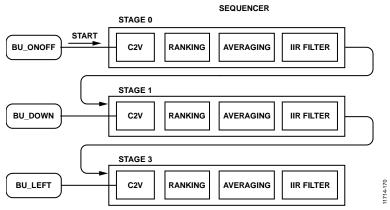

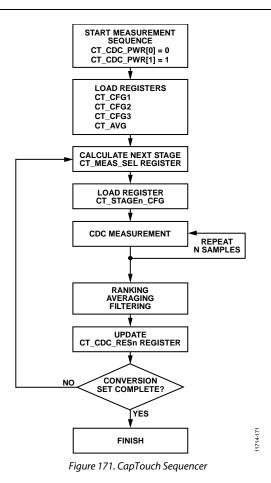

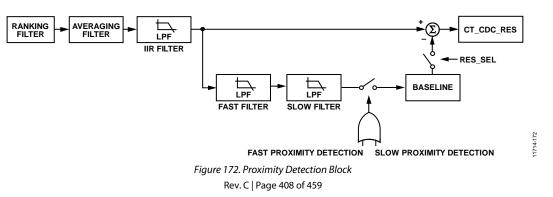

Address: 0x4000240C, Reset: 0x0000, Name: OSCKEY